Altera PCI Compiler User Manual

Page 297

Altera Corporation

User Guide Version 11.1

7–29

October 2011

Functional Description

1

Avalon-MM burst read requests are treated as if they are going

to prefetchable PCI space. Therefore, if the PCI target space is

non-prefetchable, you should not use read bursts.

There are several factors that control how Avalon-MM transactions

(bursts or single cycle) are translated to PCI transactions. These cases are

discussed in

. Remember that some optimizations are put in

place for situations where 32-bit Avalon-MM masters (for example, the

Nios

®

II processor) talk to 32-bit PCI targets through a 64-bit PCI-Avalon

bridge.

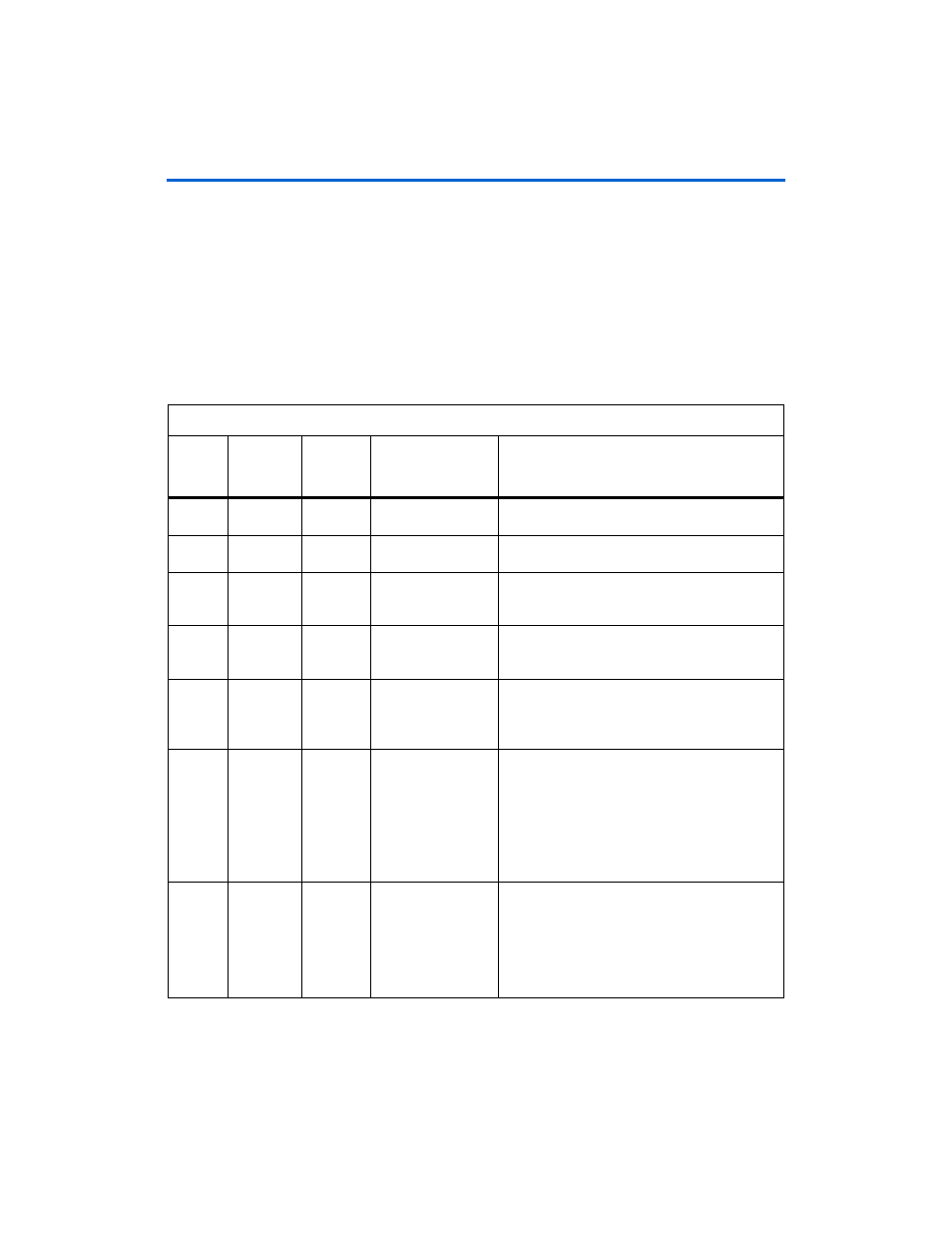

Table 7–9. Translation of Avalon Requests to PCI Requests (Part 1 of 2)

Data

Path

Width

Avalon

Burst

Count

Type of

Operation

Avalon Byte Enables

Resulting PCI Operation and Byte Enables

32

1

Read or

write

Any value

Single data phase read or write, PCI byte enables

identical to Avalon byte enables

32

>1

Read

Any value

Attempt to burst on PCI. All data phases will have

all PCI bytes enabled.

32

>1

Write

Any value

Attempt to burst on PCI. All data phases will have

PCI byte enables identical to the Avalon byte

enables.

64

1

Read and

write

Upper 4 bytes

disabled; lower 4

bytes any value

Only a single 32-bit data phase (

req64n

not

asserted) with the lower 4 byte enables sent to

PCI, and lower 32 bits of data if a write.

64

1

Read and

write

Upper 4 bytes any

value; lower 4 bytes

disabled

Only a single 32-bit data phase (

req64n

not

asserted) to the odd

DWORD

with the upper 4 byte

enables sent to PCI (and upper 32 bits of data if a

write).

64

1

Read

Bytes enabled in both

the upper and lower

DWORD

A single 64-bit data phase is attempted (

req64n

asserted) with the Avalon byte enables sent to PCI.

If the target does not assert ack64n and

disconnects after a single data phase, the

transaction is resumed as a single cycle 32-bit

request (

req64n

not asserted). The PCI byte

enables will be the upper 4 byte enables from the

original Avalon request.

64

1

Write

Bytes enabled in both

the upper and lower

DWORD

A 32-bit two data phase burst is attempted

(

req64n

not asserted) with the lower and upper

byte enables from Avalon sent in consecutive PCI

data phases.

If the target disconnects after the first data phase,

the request will be resumed as a 32-bit single data

phase transfer.