I/o read transactions – Altera PCI Compiler User Manual

Page 135

Altera Corporation

User Guide Version 11.1

3–61

October 2011

Functional Description

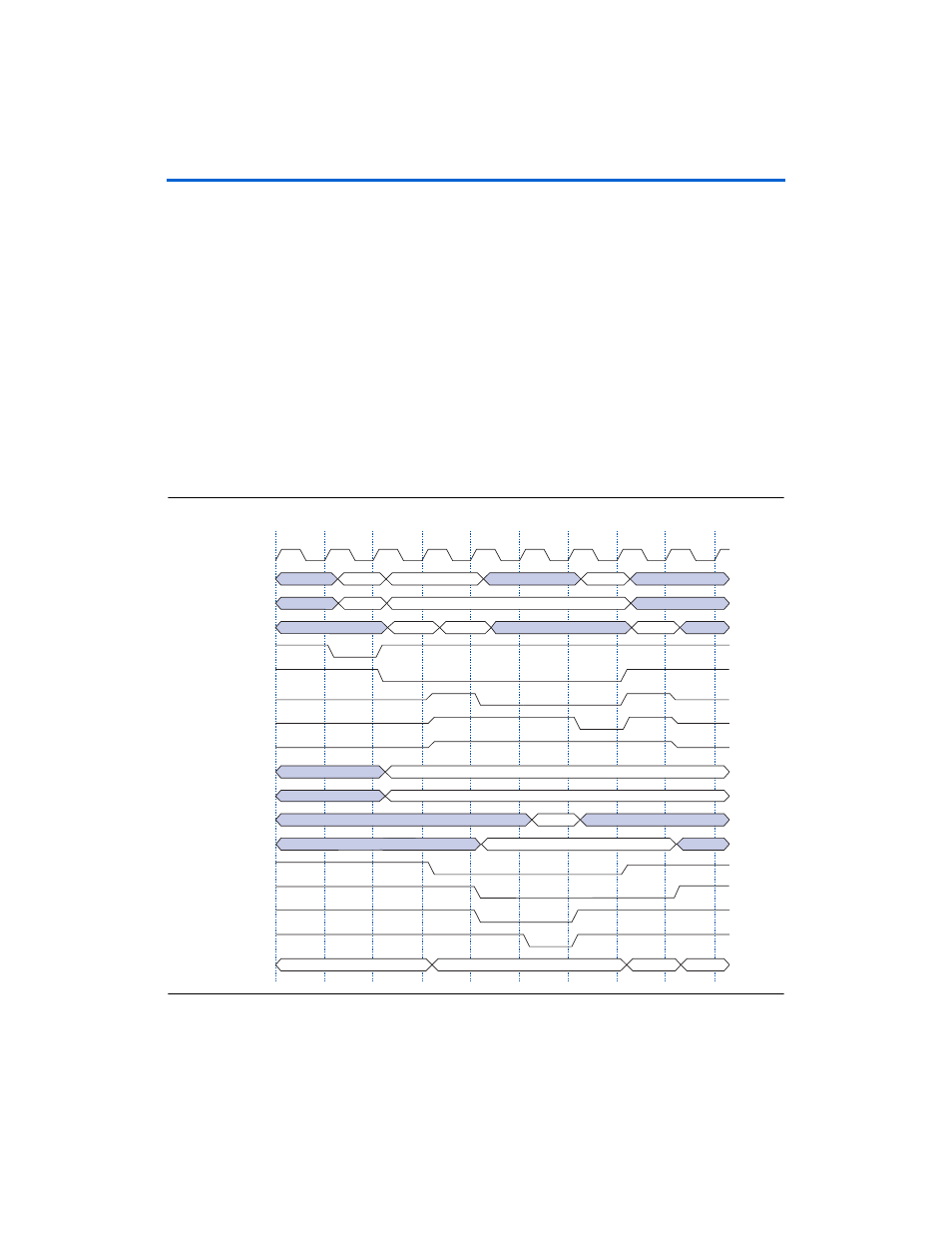

I/O Read Transactions

I/O read transactions by definition are 32 bits wide.

shows a

sample I/O read transaction. The sequence of events is the same as 32-bit

single-cycle memory read transactions. The main distinction between the

two transactions is the command on the lt_cmdo[3..0] bus. In

, lt_tsr[11..0] indicates that the base address register

that detected the address hit is BAR1. Additionally, during an I/O

transaction l_ldat_ackn and l_hdat_ackn are not relevant.

1

The PCI MegaCore functions do not ensure that the combination

of the ad[1..0] and cben[3..0] signals is valid during the

address phase of an I/O transaction. Local side logic should

implement this functionality if performing I/O transactions.

Refer to the PCI Local Bus Specification, Revision 3.0 for more

information on handling invalid combinations of these signals.

Figure 3–13. I/O Read Transaction

ad[31..0]

cben[3..0]

par

framen

irdyn

devseln

trdyn

stopn

lt_framen

l_adro[31..0]

l_cmdo[3..0]

lt_ackn

l_adi[31..0]

lt_dxfrn

clk

l_beno[3..0]

lt_tsr[11..0]

Adr

2

Adr-PAR

Z

Adr

2

BE0_L

Z

000

102

D0_L

D0-L-PAR

BE0_L

000

502

1

2

3

4

5

6

7

8

9

10

D0_L

lt_rdyn