Altera PCI Compiler User Manual

Page 323

Altera Corporation

User Guide Version 11.1

7–55

October 2011

Functional Description

lists some basic configuration parameters of the bridge.

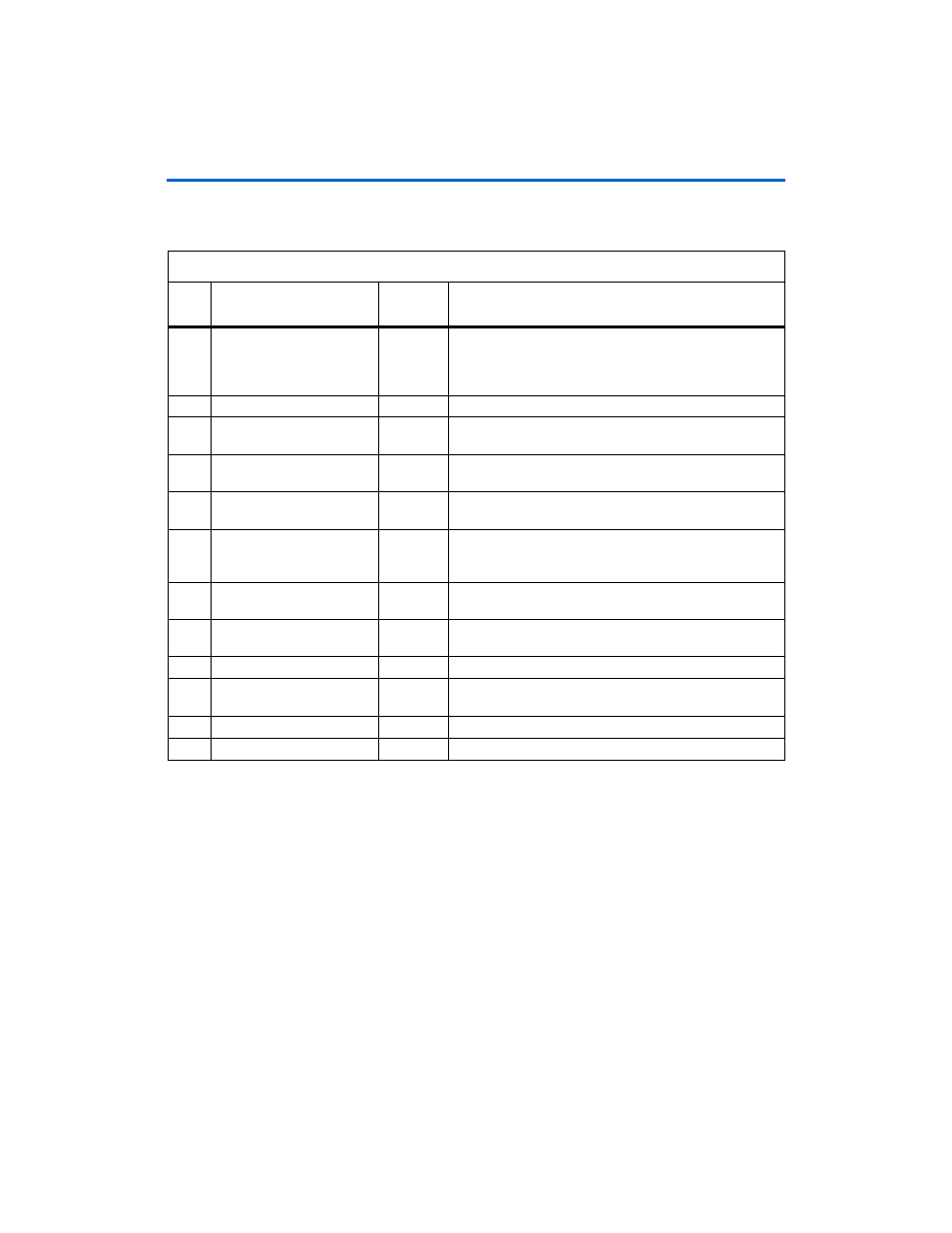

Table 7–23. General Configuration Parameters – Address 0x2C00

Bit

Name

Access

Mode

Description

6:0

PCI_ADDRESS_WIDTH

RO

Indicates whether 32- or 64-bits of PCI addressing are kept

on the Avalon-to-PCI path. Unimplemented upper bits are

always forced to 0 in the address phase of a PCI bus

transaction.

7

Reserved

RO

Reserved

8

TARGET_ONLY

RO

Indicates that you have selected the PCI Target-Only

Peripheral mode (refer to

“System Options-1” on page 6–1

9

HOST_BRIDGE_MODE

RO

Indicates that you have selected the PCI Host-Bridge Device

mode (refer to

“System Options-1” on page 6–1

).

10

PCI_BUS_64

RO

Indicates that you have selected the 64-Bit PCI Bus option

(refer to

“Value of Multiple Pending Reads” on page 6–6

).

11

COMMON_CLOCK_MODE

RO

Indicates that you have selected the Shared PCI and Avalon

Clocks option (refer to

“Value of Multiple Pending Reads” on

12

IMPL_PREF_PORT

RO

Indicates that the prefetchable Avalon-MM master port is

implemented.

13

IMPL_NONP_PORT

RO

Indicates that the non-prefetchable Avalon-MM master port

is implemented.

15:14

Reserved

RO

Reserved

19:16

NUM_A2P_MAILBOX

RO

Reflects the number of implemented Avalon-to-PCI mailbox

registers.

23:20

NUM_P2A_MAILBOX

RO

Reflects the number of PCI-to-Avalon mailbox registers.

31:24

Reserved

RO

Reserved