Altera PCI Compiler User Manual

Page 99

Altera Corporation

User Guide Version 11.1

3–25

October 2011

Functional Description

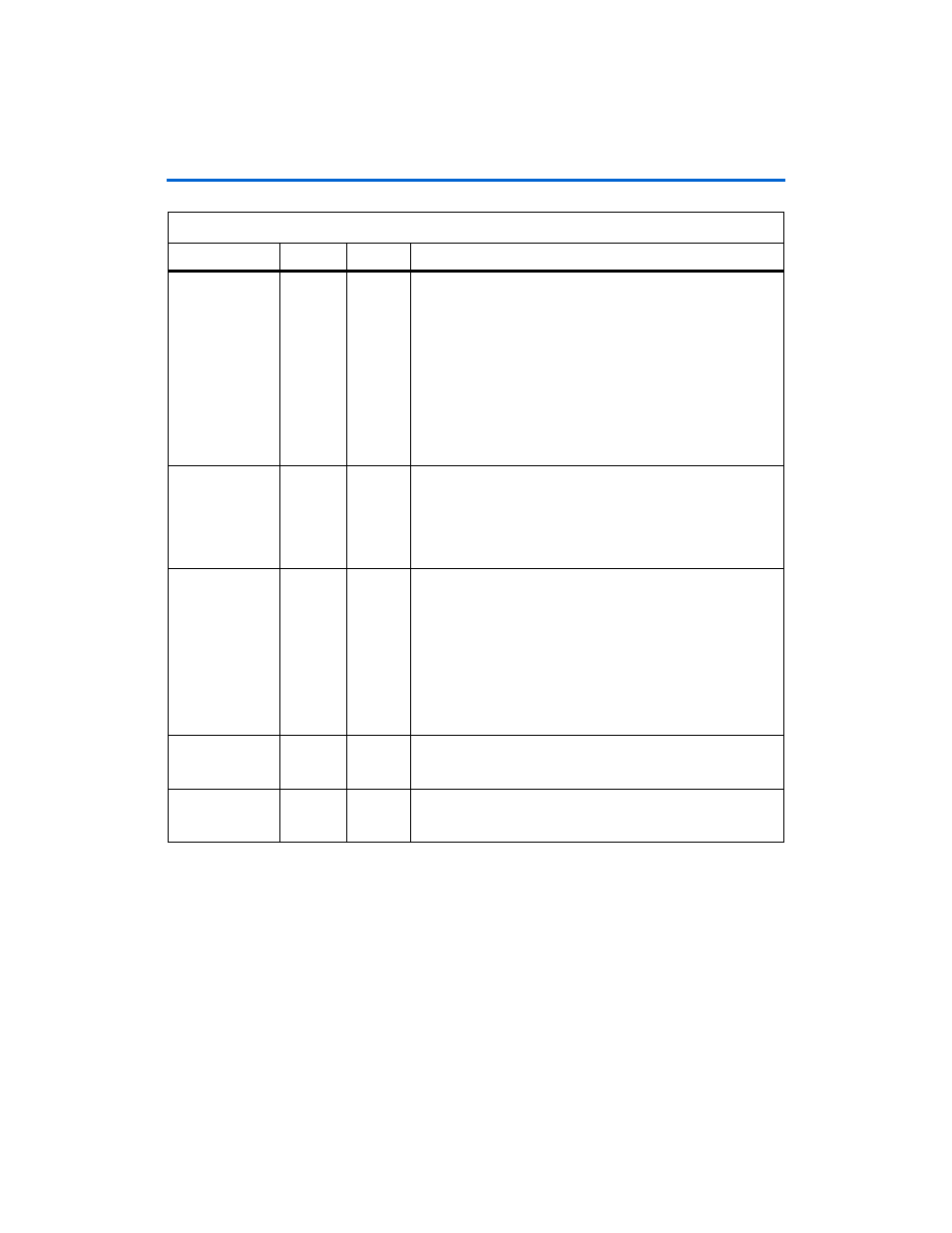

lm_rdyn

Input

Low

Local master ready. The local side asserts the

lm_rdyn

signal to

indicate a valid data input during a master write, or ready to accept

data during a master read. During a master write, the

lm_rdyn

signal de-assertion suspends the current transfer (i.e., wait state is

inserted by the local side). During a master read, an inactive

lm_rdyn

signal directs

pci_mt64

or

pci_mt32

to insert wait

states on the PCI bus. The only time

pci_mt64

or

pci_mt32

inserts wait states during a burst is when the

lm_rdyn

signal

inserts wait states on the local side.

The

lm_rdyn

signal is sampled one clock cycle before actual data

is transferred on the local side.

lm_adr_ackn

Output

Low

Local master address acknowledge.

pci_mt64

or

pci_mt32

assert the

lm_adr_ackn

signal to the local side to acknowledge

the requested master transaction. During the same clock cycle

when

lm_adr_ackn

is asserted low, the local side must provide

the transaction address on the

l_adi[31..0]

bus and the

transaction command on the

l_cmdi[3..0]

bus.

lm_ackn

Output

Low

Local master acknowledge.

pci_mt64

and

pci_mt32

assert the

lm_ackn

signal to indicate valid data output during a master read,

or ready to accept data during a master write. During a master

write, an inactive

lm_ackn

signal indicates that

pci_mt64

and

pci_mt32

is not ready to accept data, and local logic should hold

off the bursting operation. During a master read operation, the

lm_ackn

signal de-assertion suspends the current transfer (i.e., a

wait state is inserted by the PCI target). During a burst when the

PCI bus target inserts wait states, the

lm_ackn

signal goes

inactive.

lm_dxfrn

Output

Low

Local master data transfer. During a master transaction,

pci_mt64

and

pci_mt32

assert this signal when a data transfer

on the local side is successful.

lm_tsr[9..0]

Output

–

Local master transaction status register bus. These signals inform

the local interface of the transaction’s progress. Refer to

for a detailed description of the bits in this bus.

Table 3–9. PCI Master Signals Interfacing to the Local Side (Part 2 of 2)

Name

Type

Polarity

Description