Avalon-to-pci read requests, Avalon-to-pci – Altera PCI Compiler User Manual

Page 300

7–32

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

PCI Master Operation

The PCI-Avalon bridge will not combine multiple Avalon-MM writes to

consecutive locations into a single PCI write transaction. No attempt is

made to byte merge separate Avalon-MM writes that write to separate

bytes in the same DWORD or QWORD into a single PCI write operation.

The PCI interface will attempt to burst as long as it can. A PCI write burst

can be terminated for various reasons.

describes the resulting

action for the PCI master write request termination condition.

Avalon-to-PCI Read Requests

For read requests from the interconnect, the request is pushed on the PCI

bus by a configuration read, I/O read, memory read, memory read line,

or memory read multiple command. The PCI read is issued to

configuration, I/O, or memory space based on the address translation

table entry. Refer to

“Avalon-to-PCI Address Translation” on page 7–35

.

If a memory space read request can be completed in a single data phase,

it is issued as a memory read command. If the memory space read request

spans more than one data phase but does not cross a cacheline boundary

(as defined by the cacheline size register), it is issued as a memory read

line command. If the memory space read request crosses a cache line

boundary, it is issued as a memory read multiple command.

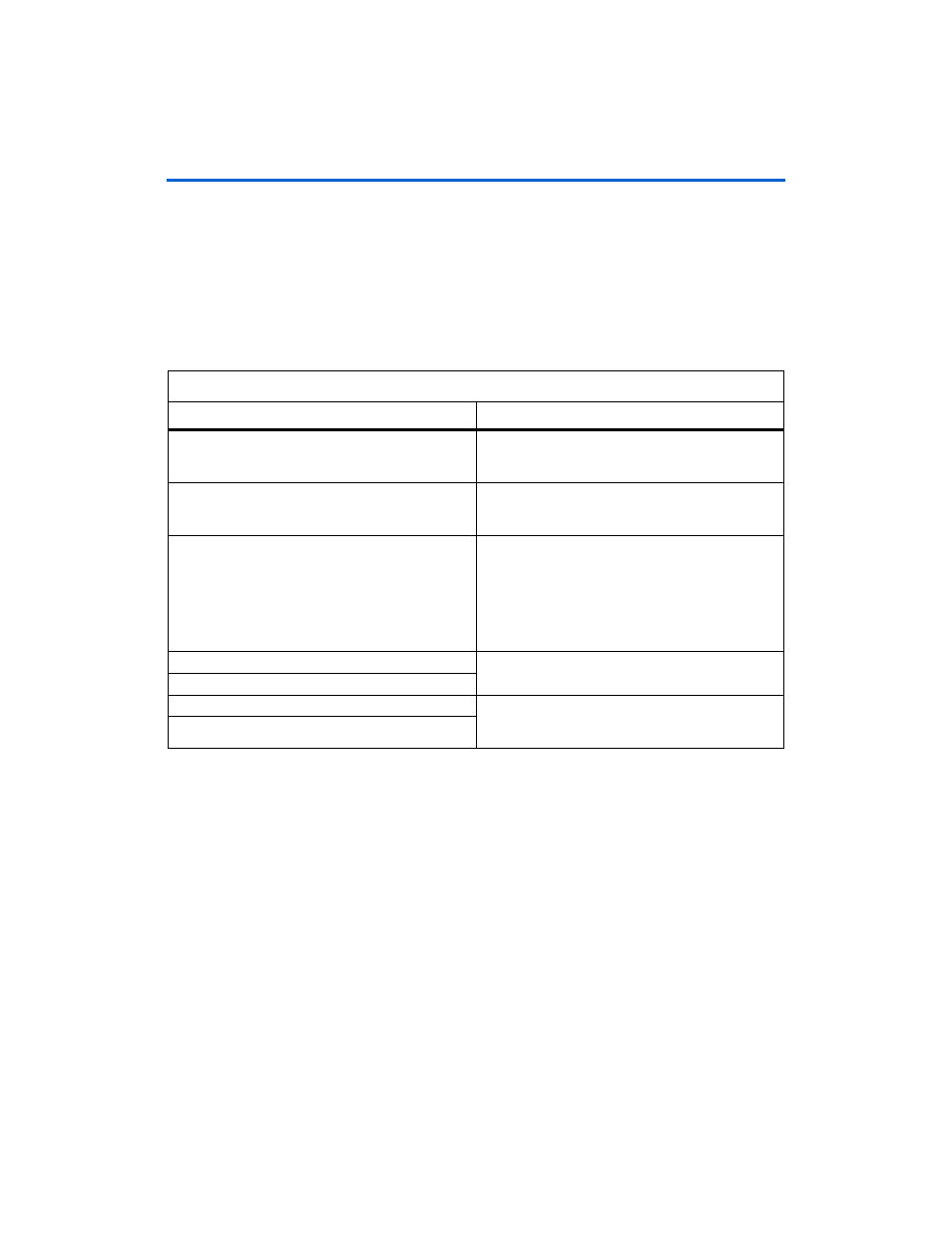

Table 7–10. PCI Master Write Request Termination Conditions

Termination condition

Resulting Action

Burst count satisfied

Normal master-initiated termination on PCI bus,

command completes, and the master controller

proceeds to the next command.

Latency timer expiring during configuration, I/O, or

memory write command

Normal master-initiated termination on PCI bus, the

continuation of the PCI write is requested from the

master controller arbiter.

Avalon-to-PCI command/write data buffer running out

of data

Normal master-initiated termination on the PCI bus.

Master controller waits for the buffer to reach 8

DWORD

s on a 32-bit PCI or 16

DWORD

s on a 64-bit PCI,

or there is enough data to complete the remaining burst

count. Once enough data is available, the continuation

of the PCI write is requested from the master controller

arbiter.

PCI target disconnect

The continuation of the PCI write is requested from the

master controller arbiter.

PCI target retry

PCI target-abort

The PCI interrupt status register bit,

ERR_PCI_WRITE_FAILURE

(bit 0), is set to 1. The rest

of the write data is read from the buffer and discarded.

PCI master-abort