Master device signals & signal assertion – Altera PCI Compiler User Manual

Page 83

Altera Corporation

User Guide Version 11.1

3–9

October 2011

Functional Description

Master Device Signals & Signal Assertion

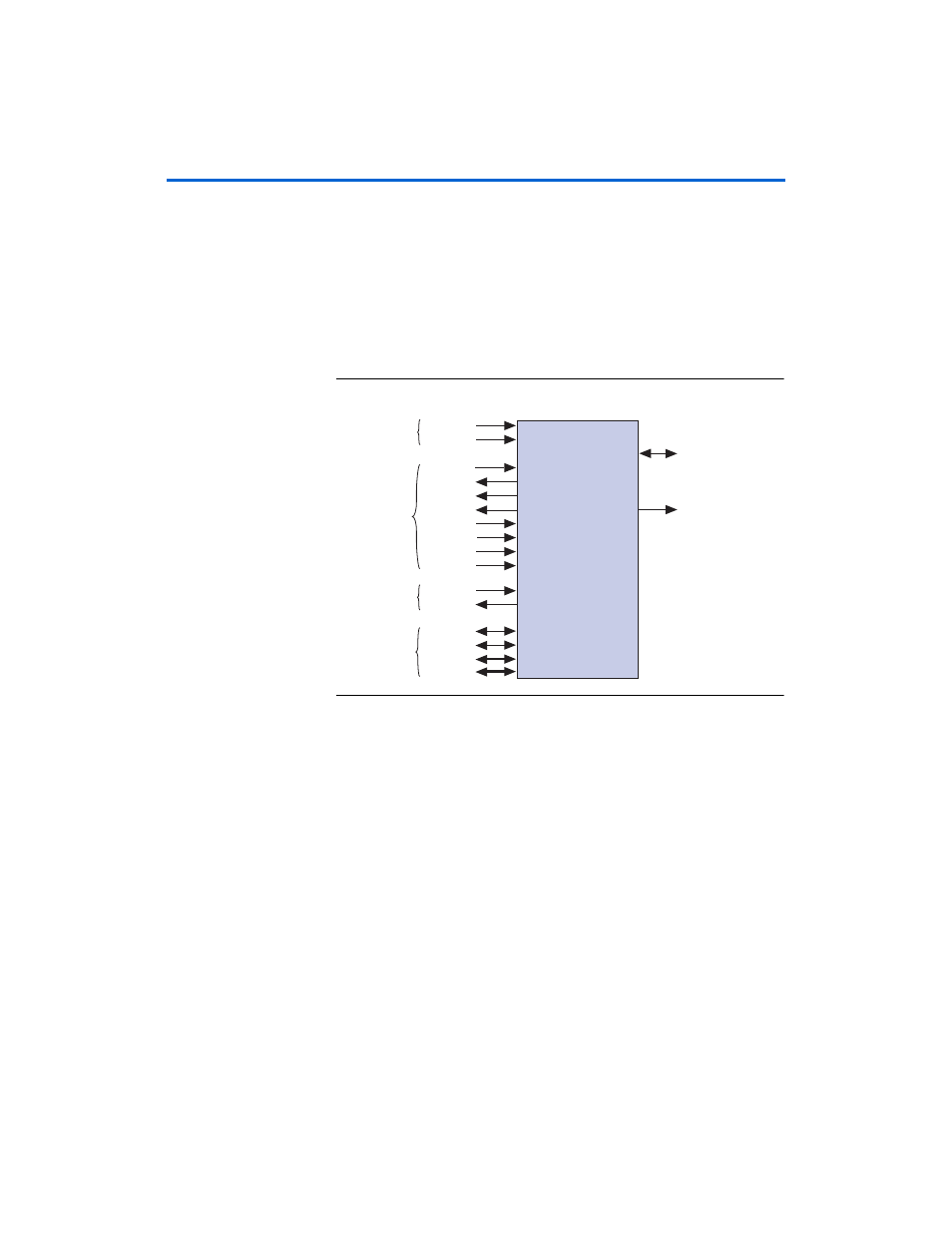

illustrates the PCI-compliant master device signals that

connect to the PCI bus. The signals are grouped by functionality, and

signal directions are illustrated from the perspective of a PCI MegaCore

function operating as a master on the PCI bus.

shows all

master signals. The 64-bit extension signals, including req64n, ack64n,

par64

, ad[63..32], and cben[7..4], are not implemented in the

pci_mt32

function.

Figure 3–6. Master Device Signals

A 32-bit master sequence begins when the local side asserts lm_reqn32n

to request mastership of the PCI bus. The PCI MegaCore function then

asserts reqn to request ownership of the PCI bus. After receiving gntn

from the PCI bus arbiter and after the bus idle state is detected, the

function initiates the address phase by asserting framen, driving the PCI

address on ad[31..0], and driving the bus command on cben[3..0]

for one clock cycle.

1

For 64-bit addressing, the master generates a dual-address cycle

(DAC). On the first address phase, the pci_mt64 function

drives the lower 32-bit PCI address on ad[31..0], the upper

32-bit PCI address on ad[63..32], the DAC command on

cben[3..0]

, and the transaction command on cben[7..4].

On the second address phase, the pci_mt64 function drives the

upper 32-bit PCI address on ad[31..0] and the transaction

command on cben[3..0].

Master Device

clk

rstn

idsel

req64n

framen

irdyn

trdyn

stopn

devseln

ack64n

par64

par

ad[63..0]

cben[7..0]

perrn

intan

System

Signals

Interface

Control

Signals

Address,

Data &

Command

Signals

Interrupt

Request

Signal

gntn

reqn

Arbitration

Signals

Error

Reporting

Signal