Altera PCI Compiler User Manual

Page 86

3–12

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

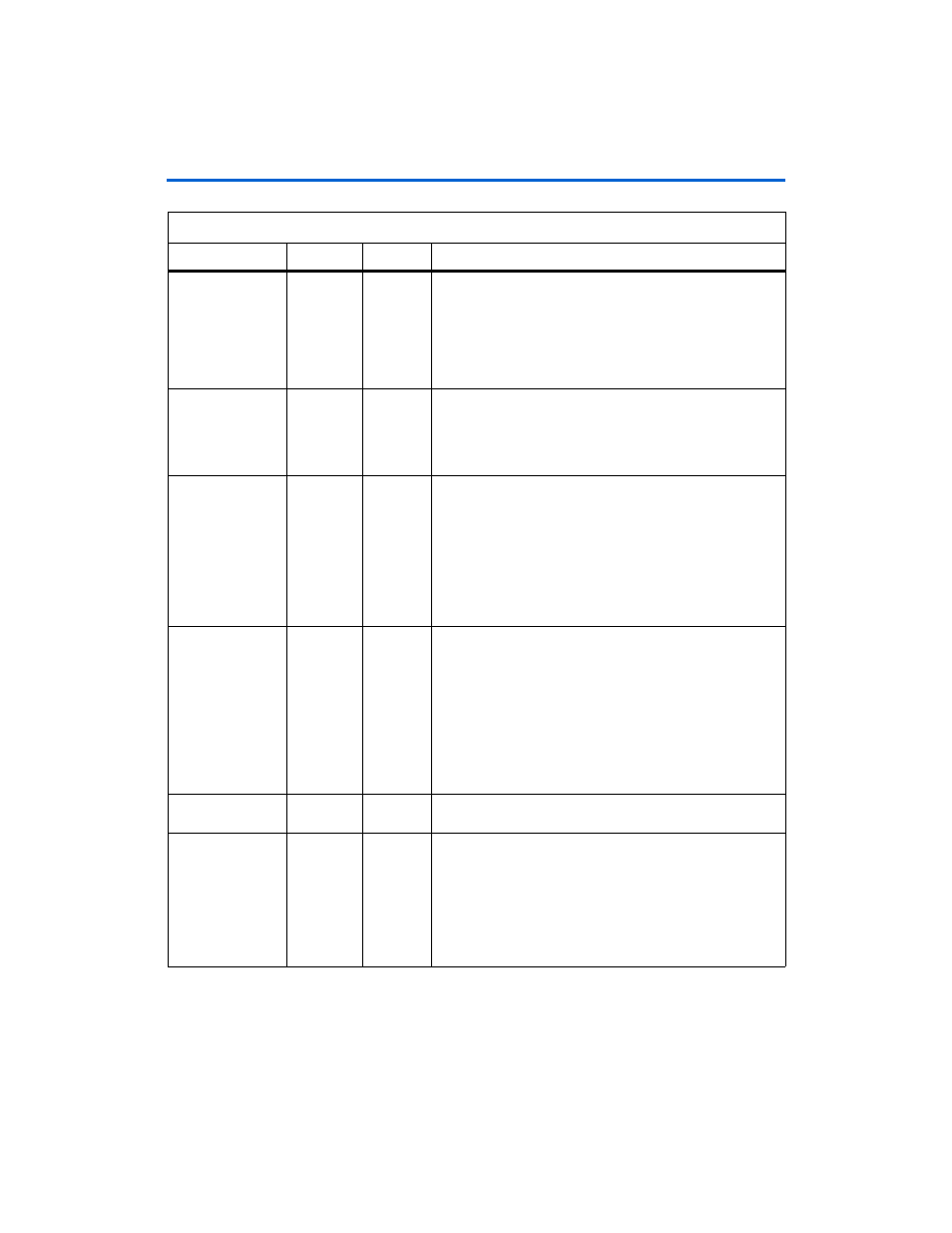

PCI Bus Signals

ad[63..0]

Tri-State

–

Address/data bus. The

ad[63..0]

bus is a time-multiplexed

address/data bus; each bus transaction consists of an address

phase followed by one or more data phases. The data phases

occur when

irdyn

and

trdyn

are both asserted. In the case

of a 32-bit data phase, only the

ad[31..0]

bus holds valid

data. For

pci_mt32

and

pci_t32

, only

ad[31..0]

is

implemented.

cben[7..0]

Tri-State

–

Command/byte enable. The

cben[7..0]

bus is a time-

multiplexed command/byte enable bus. During the address

phase, this bus indicates the command. During the data phase,

this bus indicates byte enables. For

pci_mt32

and

pci_t32

,

only

cben[3..0]

is implemented.

par

Tri-State

–

Parity. The

par

signal is even parity across the 32 least

significant address/data bits and four least significant

command/byte enable bits, i.e., the number of 1s on

ad[31..0]

,

cben[3..0]

, and

par

equal an even number.

The

par

signal is valid one clock cycle after each address

phase. For data phases,

par

is valid one clock cycle after either

irdyn

asserted on a write transaction or trdyn is asserted on

a read transaction. Once

par

is valid, it remains valid until one

clock cycle after the current data phase.

par64

Tri-State

–

Parity 64. The

par64

signal is even parity across the 32 most

significant address/data bits and the four most significant

command/byte enable bits, i.e., the number of 1s on

ad[63..32]

,

cben[7..4]

, and

par64

equal an even

number. The

par64

signal is valid one clock cycle after the

address phase where

req64n

is asserted. For data phases,

par64

is valid one clock cycle after either

irdyn

is asserted

on a write transaction or

trdyn

is asserted on a read

transaction. This signal is not implemented in the

pci_mt32

and

pci_t32

functions.

idsel

Input

High

Initialization device select. The

idsel

input is a chip select for

configuration transactions.

framen

STS

Low

Frame. The

framen

signal is an output from the current bus

master that indicates the beginning and duration of a bus

operation. When

framen

is initially asserted, the address and

command signals are present on the

ad[63..0]

and

cben[7..0]

buses (

ad[31..0]

and

cben[3..0]

only for

32-bit functions). The

framen

signal remains asserted during

the data operation and is deasserted to identify the end of a

transaction.

Table 3–2. PCI Interface Signals (Part 2 of 4)

Name

Type

Polarity

Description