Non-prefetchable operations – Altera PCI Compiler User Manual

Page 285

Altera Corporation

User Guide Version 11.1

7–17

October 2011

Functional Description

■

Read requests will always be initially retried and completed as

delayed read operations.

■

The requests will be directed to the prefetchable Avalon-MM master

port. The data path between the PCI bus and this Avalon-MM port

will be optimized to support higher bandwidth that results in higher

latency to transition through the required RAM buffers.

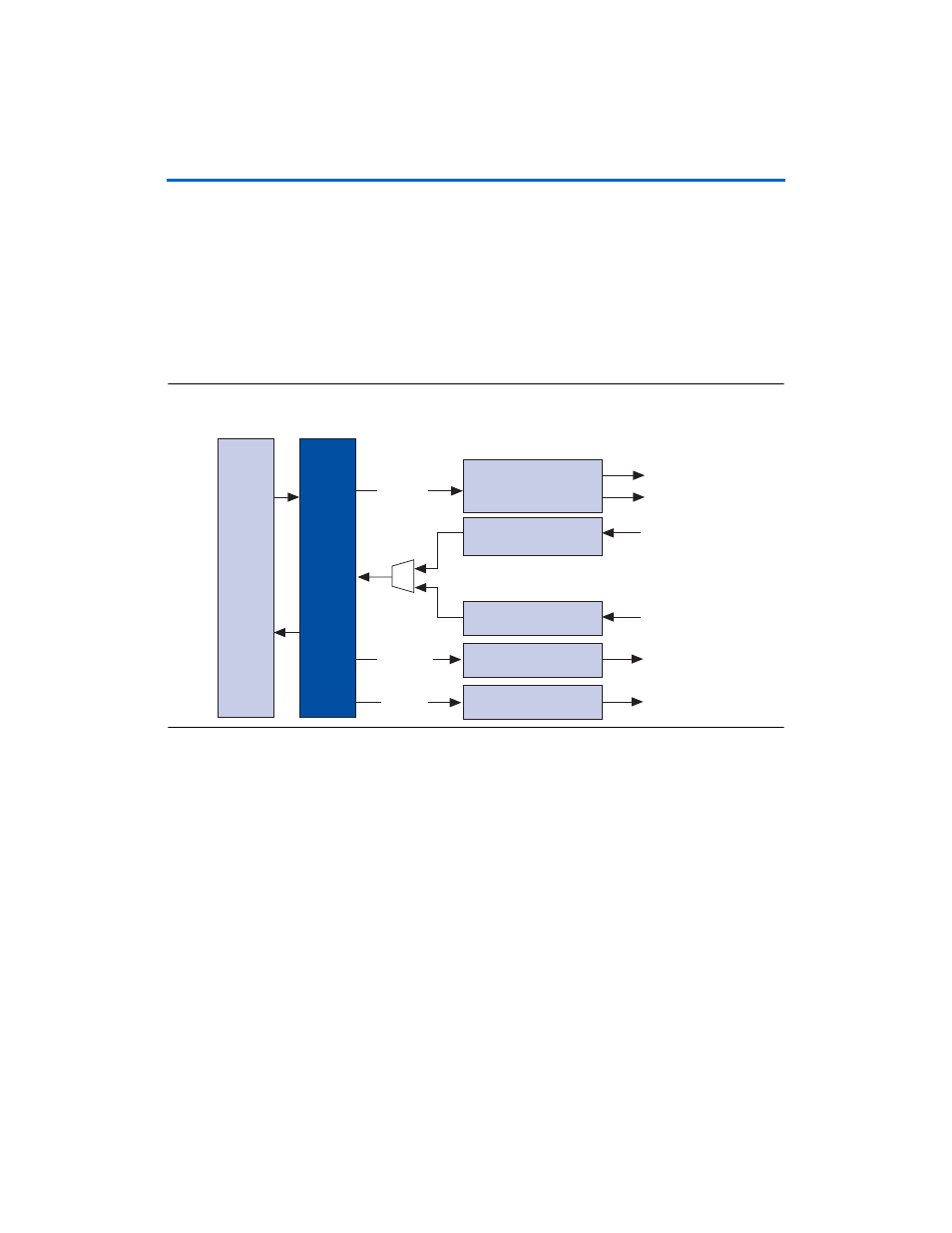

shows the bridge logic between the PCI target controller and

Avalon-MM master ports.

Figure 7–7. PCI Target-to-Avalon-MM Master Block Diagram

Non-Prefetchable Operations

Non-prefetchable operations are defined as either transactions that hit:

■

A non-prefetchable BAR

■

A prefetchable BAR if the Single-Cycle Transfers Only target

performance profile is used

As previously noted, PCI write operations involve only one PCI

transaction where the address/command and data is transferred. The

read operation involves at least two PCI transactions. In the first PCI

transaction (request), the address and data are transferred to the

PCI-Avalon bridge, and in the second transaction (completion), the

PCI-Avalon bridge transfers the data.

PCI

MegaCore

Function

Prefetchable

Addr/Data

Write Data

Address

Write Data

Read Data

Read Data

Prefetchable

Avalon Master Port

Non-Prefetchable

Avalon Master Port

Prefetchable

Command/Write

Data Buffer

Prefetchable Read

Response Data Buffer

Address

Non-Prefetchable

Command Register

Non-Prefetchable

Write Data Register

PCI

Target

Controller

Non-Prefetchable

Read Response Register

Non-Prefetchable

Write Data

Non-Prefetchable

Address