Status register – Altera PCI Compiler User Manual

Page 107

Altera Corporation

User Guide Version 11.1

3–33

October 2011

Functional Description

Status Register

Status is a 16-bit register that provides the status of bus-related events.

Read transactions from the status register behave normally. However,

status register write transactions are different from typical write

transactions because bits in the status register can be cleared but not set.

A bit in the status register is cleared by writing a logic one to that bit. For

example, writing the value 0x4000 to the status register clears bit 14 and

leaves the rest of the bits unchanged. The default value of the status

register is 0x0400. Refer to

.

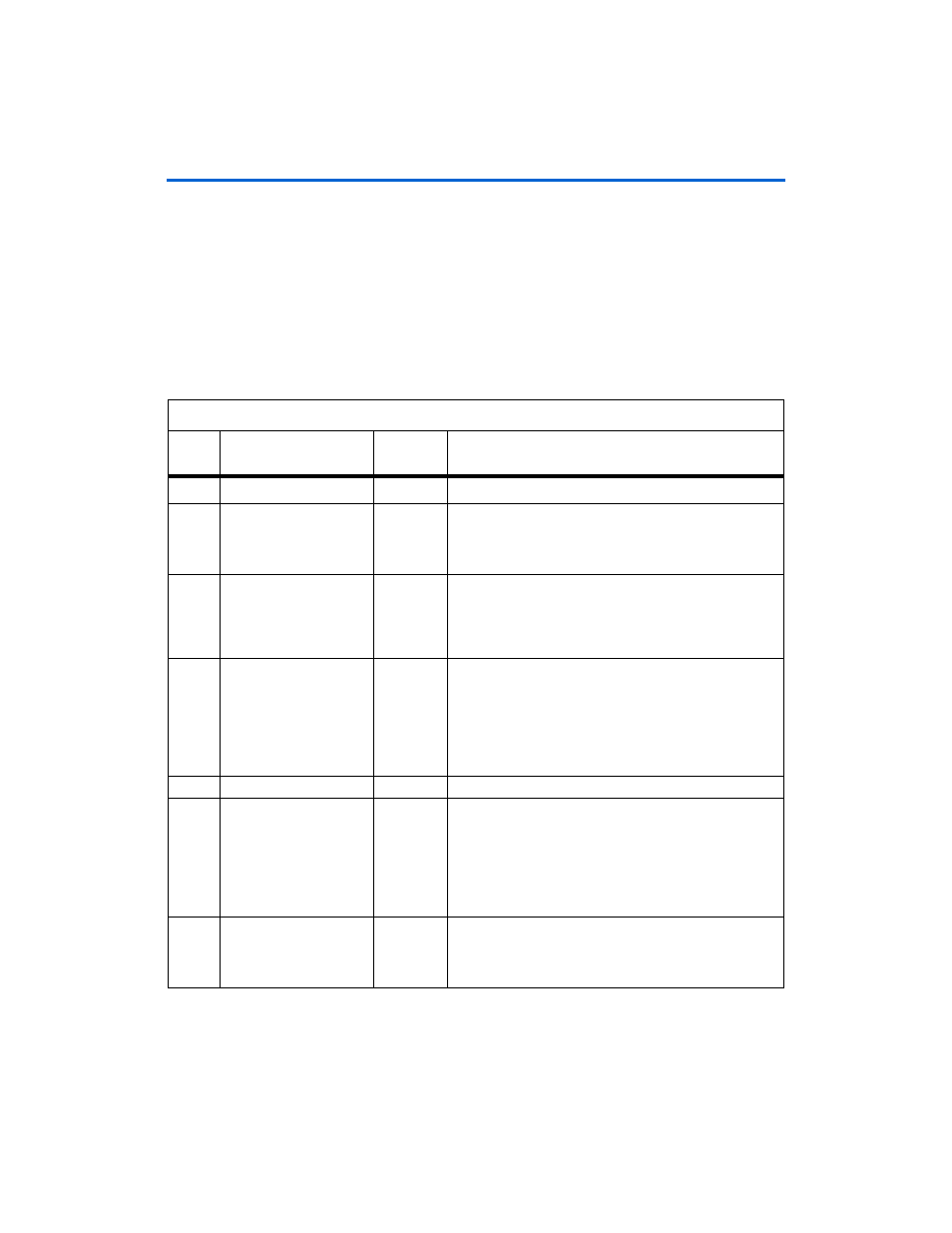

Table 3–17. Status Register Format (Part 1 of 2)

Data

Bit

Mnemonic

Read/Write

Definition

2..0

Unused

–

Reserved.

3

int_stat

Read

Interrupt status. This bit is read only and is set when the

int_dis

bit (bit 10 of the command register) is 0 and

intan

is asserted on the PCI bus. This signal is driven to

the local side on the

stat_reg[6]

output.

4

cap_list_ena

Read

Capabilities list enable. This bit is read only and is set by the

user when enabling the Capabilities List Pointer through

the wizard. When set, this bit enables the capabilities list

pointer register at offset 0x34. Refer to

for more details.

5

pci_66mhz_capable

Read

PCI 66-MHz capable. When set,

pci_66mhz_capable

indicates that the PCI device is capable of running at 66

MHz. The PCI MegaCore functions can function at either 66

MHz or 33 MHz depending on the device used. You can set

this bit to

1

by turning on PCI 66MHz Capable on the initial

page of the IP Toolbench Parameterize - PCI Compiler

wizard.

7..6

Unused

–

Reserved.

8

dat_par_rep

Read/write

Reported data parity. When high,

dat_par_rep

indicates

that during a read transaction the function asserted the

perrn

output as a master device, or that during a write

transaction the

perrn

output was asserted as a target

device. This bit is high only when the

perr_ena

bit (bit 6 of

the command register) is also high. This signal is driven to

the local side on the

stat_reg[0]

output.

10..9

devsel_tim

Read

Device select timing. The

devsel_tim

bits indicate target

access timing of the function via the

devseln

output. The

PCI MegaCore functions are designed to be slow target

devices (i.e.,

devsel_tim = B"10

"

).