R to – Altera PCI Compiler User Manual

Page 325

Altera Corporation

User Guide Version 11.1

7–57

October 2011

Functional Description

describes the Avalon-MM interrupt status register bits.

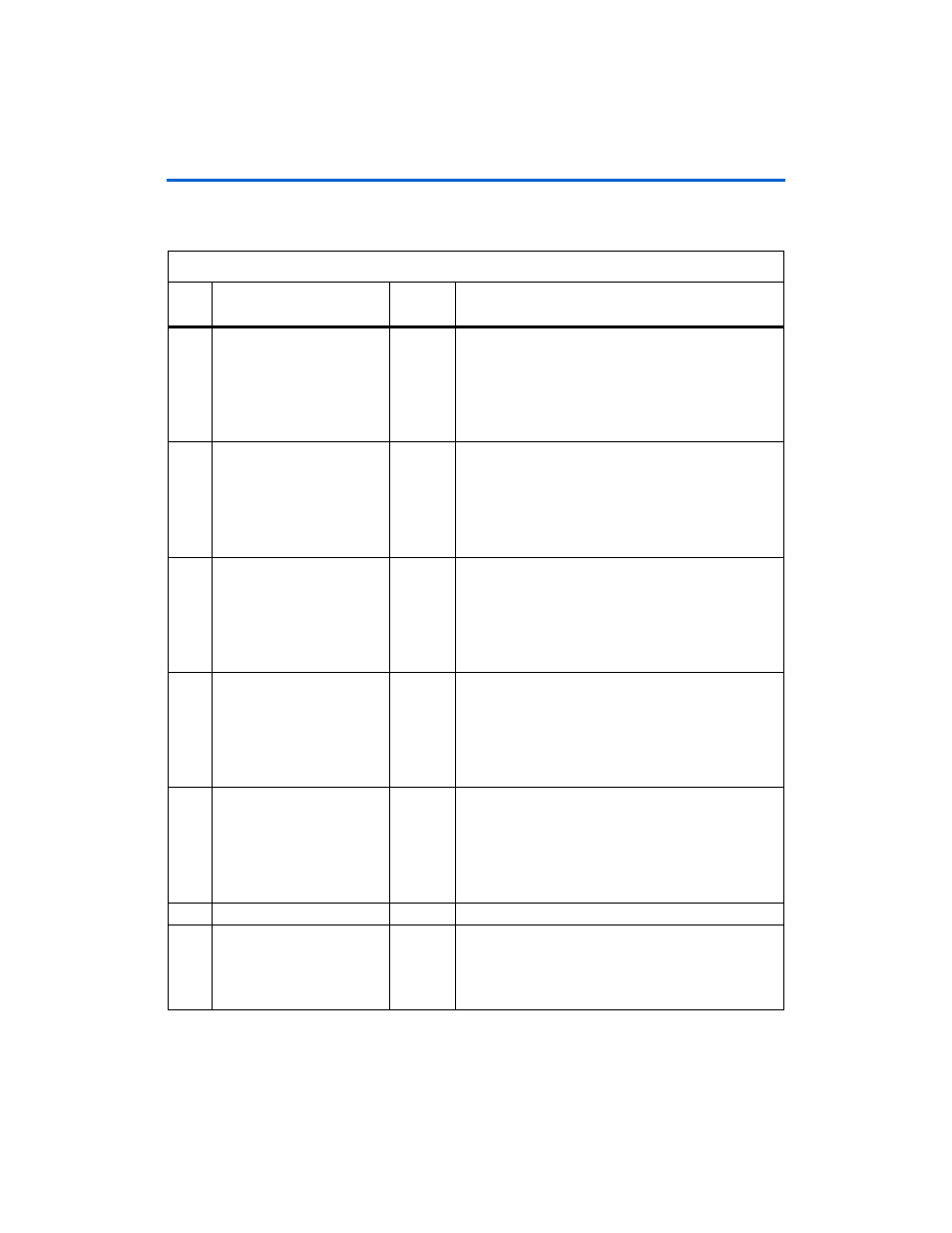

Table 7–26. Avalon Interrupt Status Register – Address 0x3060 (Part 1 of 2)

Bit

Name

Access

Mode

Description

0

ERR_PCI_WRITE_FAILURE

RW1C

When set to 1 indicates a write to PCI failure either due to

a master or target abort, or because the retry threshold has

been exceeded. This bit can also be cleared by writing '1'

to the same bit in the PCI interrupt status register.

This bit will only be implemented when the bridge is

operating in the PCI Master/Target Peripheral modes or

the PCI Host-Bridge Device mode.

1

ERR_PCI_READ_FAILURE

RW1C

When set to 1 indicates a read from PCI failure either due

to a master or target abort, or because the retry threshold

has been exceeded. This bit can also be cleared by writing

'1' to the same bit in the PCI interrupt status register.

This bit will only be implemented when the bridge is

operating in the PCI Master/Target Peripheral modes or

the PCI Host-Bridge Device mode.

2

ERR_NONP_DATA_DISCARD

RW1C

When set to 1 indicates that non-prefetchable data read

from the interconnect is discarded because the PCI read

request was not retried before the parameterized discard

timer expired. This bit can also be cleared by writing '1' to

the same bit in the PCI interrupt status register.

This bit will only be implemented when the

non-prefetchable Avalon-MM master port is implemented.

3

MASTER_ENABLE_FALL

RW1C

This bit is set to 1 when the PCI command register master

enable bit (command register bit 2) falls from 1 to 0. This

bit is set to 0 when '1' is written to it and master enable does

not transition in the same cycle as the write.

This bit is only implemented when the bridge is operating

in the PCI Master/Target Peripheral modes or the PCI

Host-Bridge Device mode.

4

MASTER_ENABLE_RISE

RW1C

This bit is set to 1 when the PCI command register master

enable bit (command register bit 2) rises from 0 to 1. This

bit is set to 0 when '1' is written to it and master enable does

not transition in the same cycle as the write.

This bit is only implemented when the bridge is operating

in the PCI Master/Target Peripheral modes or the PCI

Host-Bridge Device mode.

5

Reserved

N/A

6

INTAN_FALL

RW1C

This bit is set to 1 when the PCI

intan

signal changes

from 1 to 0. This bit is set to 0 when '1' is written to it and

intan

does not transition in the same cycle as the write.

This bit is only implemented when the bridge is operating

in the PCI Host-Bridge Device mode.