Io_wr, Io_rd, Target transactor (trgt_tranx) – Altera PCI Compiler User Manual

Page 222

4–12

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Testbench Specifications

io_wr

The io_wr command performs a single-cycle memory write transaction

with the address and data provided in the command arguments.

io_rd

The io_rd command performs single-cycle I/O read transactions with

the address provided in the command argument.

Target Transactor (trgt_tranx)

The target transactor simulates the behavior of a target agent on the PCI

bus. The master transactions initiated by the Altera PCI MegaCore

function under test should be addressed to the target transactor. The

target transactor operates in 32- or 64-bit mode. The target transactor

implements two base address registers BAR0 and BAR1 as shown in

.

For definitions of the target transactor address space, refer to the base

address registers in

Table 4–8, “Memory Map,” on page 16.

The memory range reserved by BAR0 is defined by the address_lines

and mem_hit_range settings in the target transactor source code.

The target transactor has a 32-bit register that stores data for I/O

transactions. This register is mapped to BAR1 of the configuration

address space. Because this is the only register that is mapped to BAR1,

Syntax:

io_wr(address, data)

Arguments:

address

Transaction address. This value must be

in hexadecimal radix.

data

Data written during the transaction. This

value must be in hexadecimal radix.

Syntax:

io_rd(address)

Arguments:

address

Transaction address. This value must be in

hexadecimal radix.

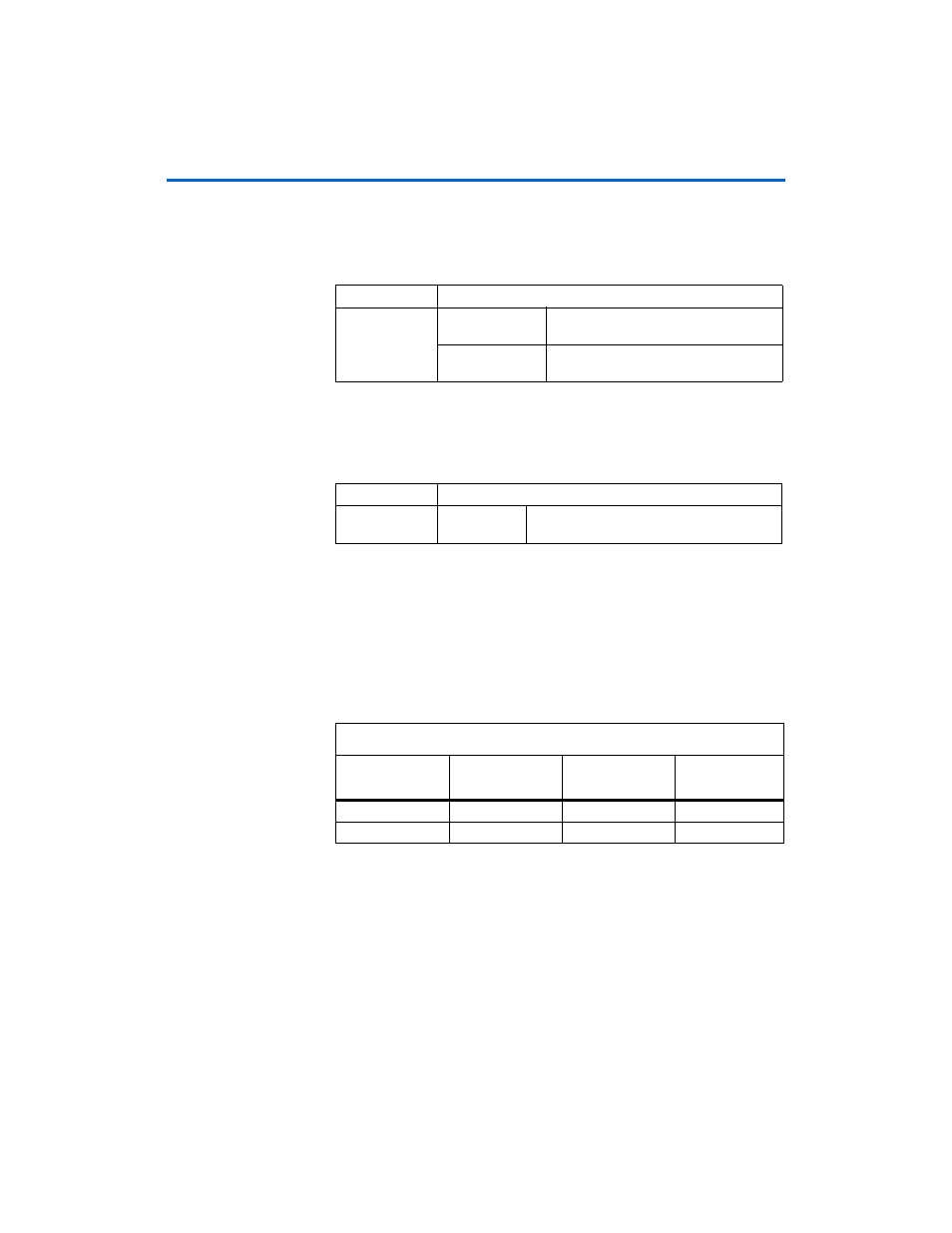

Table 4–7. Target Transactor Address Space Allocation

Configuration

Register

Address Space

Type

Block Size

Address Offset

BAR0

Memory Mapped

1 KByte

000-3FF

BAR1

I/O Mapped

16 Bytes

0-F