Pci bus arbiter signals – Altera PCI Compiler User Manual

Page 282

7–14

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Interface Signals

requirements. If you use the PCI constraint files as recommended, the

SOPC Builder reset signal will be assigned to the PCI reset signal and all

PCI settings will automatically be made in your Quartus II project file.

Depending on the selected clock option, you may have one or more clock

signals in your SOPC Builder system. There are two clock options (refer

to

“Value of Multiple Pending Reads” on page 6–6

):

■

If you select Shared PCI and Avalon Clocks, the resulting SOPC

Builder system will have only one clock signal, clk. This pin must be

connected to your device’s PCI clock signal and must have all of the

appropriate PCI assignments in your Quartus II project. The PCI

constraint files do not make the appropriate assignments.

■

If you select Independent PCI and Avalon Clocks, the resulting

SOPC Builder system will have at least two clock signals, clk and

clk_

<pci_compiler_instance_name>. The latter of these signals must

be connected to your device’s PCI clock signal on your device and

must have the appropriate PCI assignments in your Quartus II

project. You can use the PCI constraint files to make all of the

appropriate PCI assignments.

f

For more information on using PCI constraint files, refer to

Using PCI Constraint File Tcl Scripts

PCI Bus Arbiter Signals

lists the PCI arbiter interface signals. These signals are only

present when the Altera-Provided Arbiter Internal to Device option is

selected in the PCI bus arbiter field (refer to

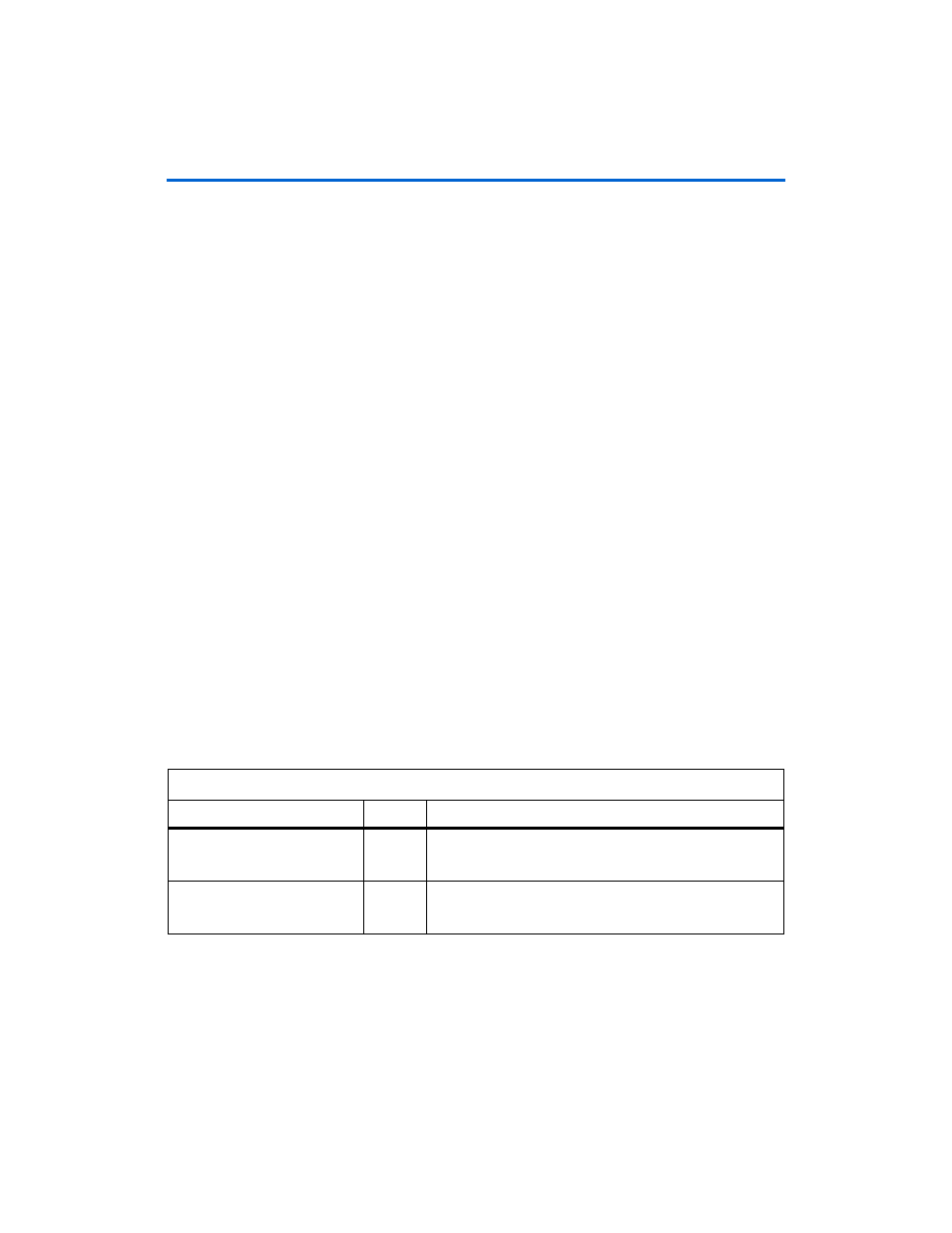

Table 7–2. PCI Arbiter Ports

Name

Type

Description

ArbReq_n_i[N-1]

Input

Bus request inputs. These signals are asserted when the

connected agent wants to master the PCI bus. Where N is the

number of PCI devices supported by the arbiter.

ArbGnt_n_o[N-1]

Output

Bus grant outputs. These signals are asserted when the bus is

granted to one of the attached devices. Where N is the number

of PCI devices supported by the arbiter.