Altera PCI Compiler User Manual

Page 126

3–52

User Guide Version 11.1

Altera Corporation

PCI Compiler

October 2011

Target Mode Operation

1

The local-side design must ensure that PCI latency rules are not

violated while the PCI MegaCore function waits for data. If the

local-side design is unable to meet the latency requirements, it

must assert lt_discn to request that the PCI MegaCore

function terminate the transaction. The PCI target latency rules

state that the time to complete the first data phase must not be

greater than 16 clock cycles, and the subsequent data phases

must not take more than 8 clock cycles to complete.

8

The PCI MegaCore function deasserts

trdyn

,

devseln

, and

ack64n

to end the

transaction. To satisfy the requirements for sustained tri-state buffers, the PCI MegaCore

function drives

devseln

,

ack64n

,

trdyn

, and

stopn

high during this clock cycle.

Additionally, the PCI MegaCore function tri-states the

ad

bus because the cycle is complete.

The rising edge of clock cycle 8 signals the end of the last data phase because

framen

is

deasserted and

irdyn

and

trdyn

are asserted. In clock cycle 8, the PCI MegaCore function

also informs the local side that no more data is required by deasserting

lt_framen

, and

lt_tsr[10]

is asserted to indicate a successful data transfer on the PCI side during the

previous clock cycle.

9

The PCI MegaCore function informs the local-side device that the transaction is complete by

deasserting the

lt_tsr[11..0]

signals. Additionally, the PCI MegaCore function tri-states

devseln

,

ack64n

,

trdyn

, and

stopn

to begin the turn-around cycle on the PCI bus.

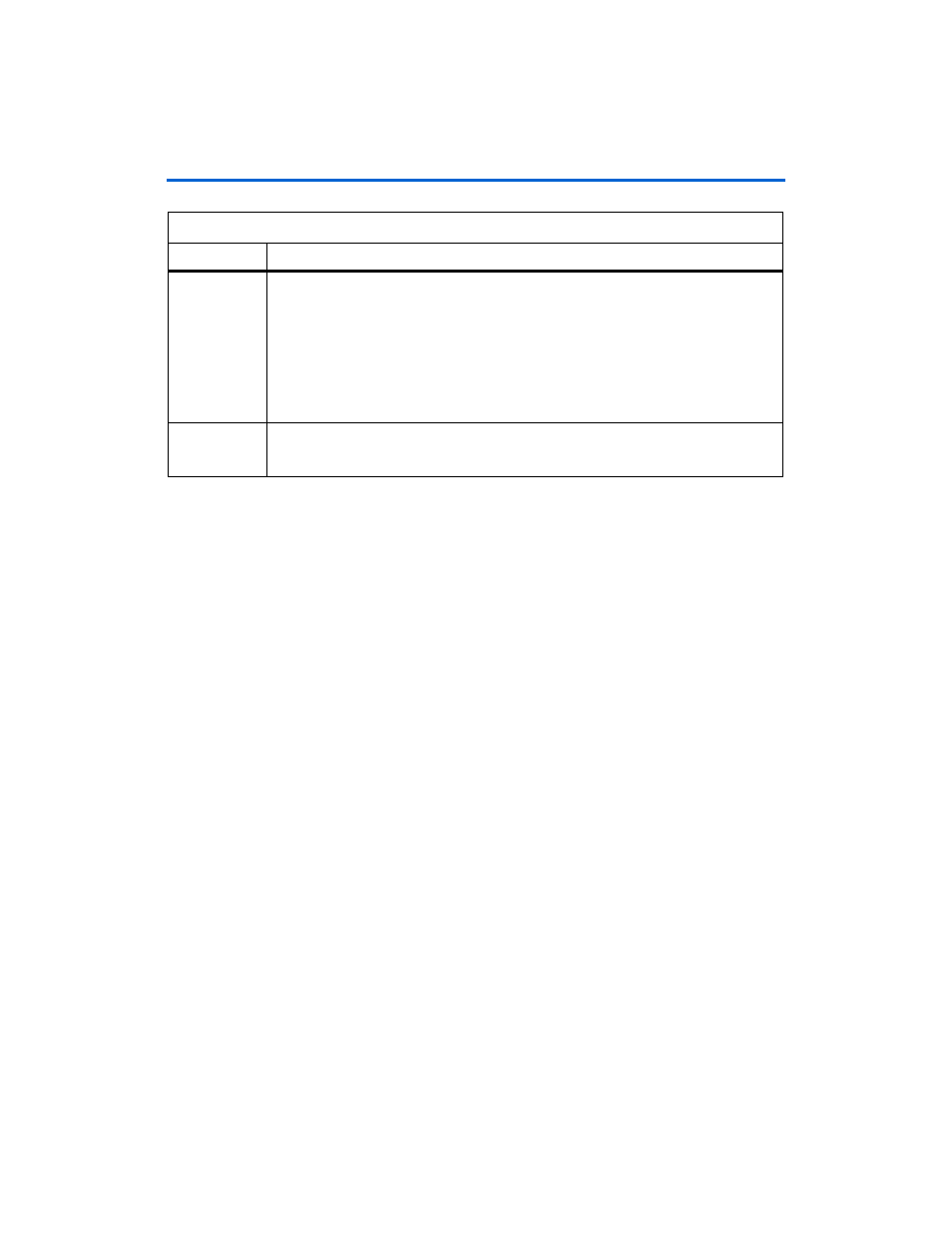

Table 3–35. Single-Cycle Memory Read Target Transaction (Part 2 of 2)

Clock Cycle

Event