Pci interrupt enable register – Altera PCI Compiler User Manual

Page 319

Altera Corporation

User Guide Version 11.1

7–51

October 2011

Functional Description

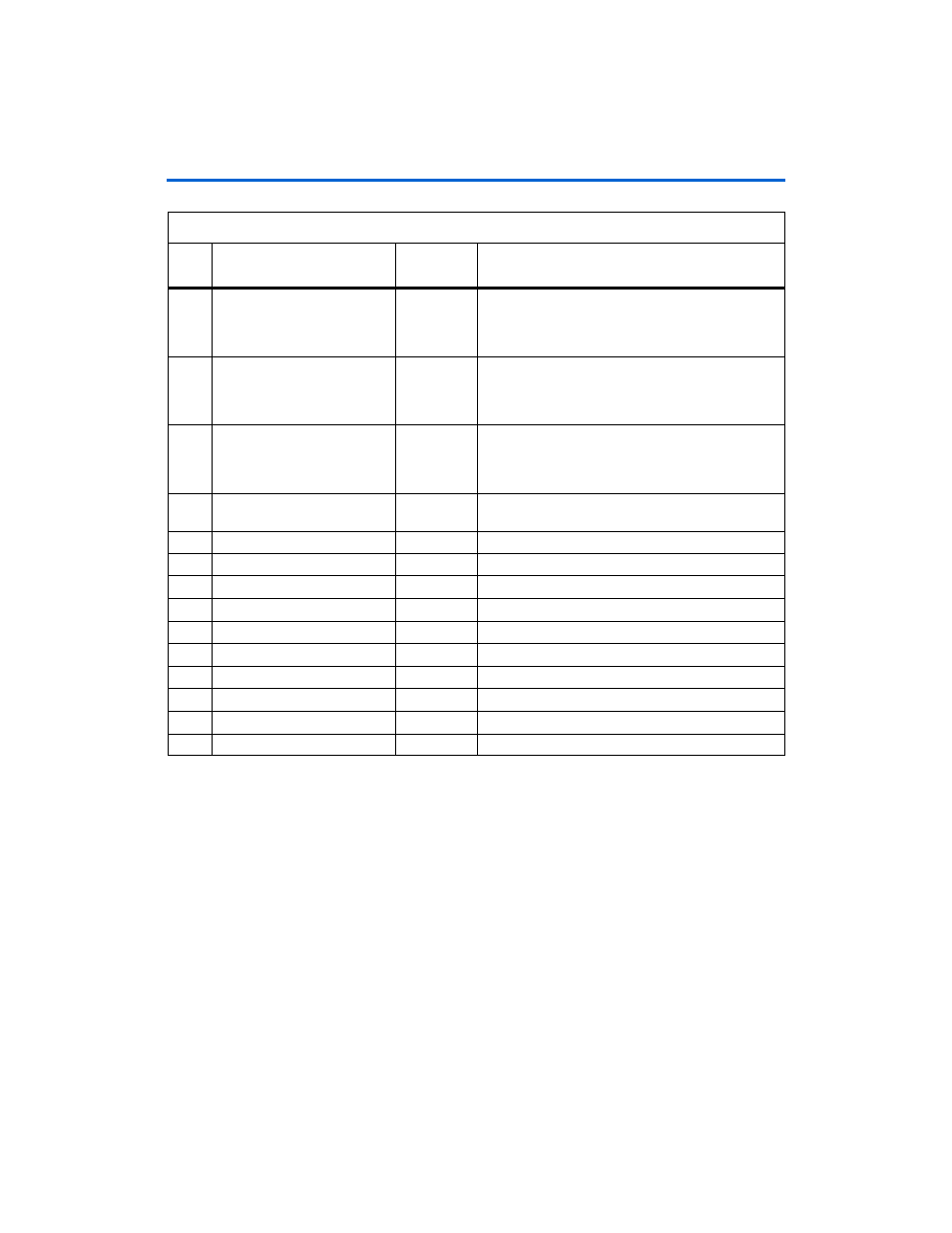

PCI Interrupt Enable Register

By setting the corresponding bits in the PCI interrupt enable register, a

PCI interrupt can be signaled for any of the conditions registered in the

PCI interrupt status register (

). The PCI interrupt enable

register has one-to-one mapping to the PCI interrupt status register.

10

PCI_TABORT_RCVD

RO

Reflects the current value of PCI status register bit 12,

target abort received. This bit can only be cleared

through a direct access to the PCI configuration status

register.

11

PCI_MABORT_RCVD

RO

Reflects the current value of PCI configuration status

register bit 13, master abort received. This bit can only

be cleared through a direct access to the PCI

configuration status register.

12

PCI_SERR_SIG

RO

Reflects the current value of PCI configuration status

register bit 14, system error signaled. This bit can only

be cleared through a direct access to the PCI

configuration status register.

13

PCI_PERR_DET

RO

Reflects the current value of PCI configuration status

register bit 15,

PERR

detected.

15:14

Reserved

N/A

16

A2P_MAILBOX_INT0

RW1C

Set to 1 when the

A2P_MAILBOX0

is written to.

17

A2P_MAILBOX_INT1

RW1C

Set to 1 when the

A2P_MAILBOX1

is written to.

18

A2P_MAILBOX_INT2

RW1C

Set to 1 when the

A2P_MAILBOX2

is written to.

19

A2P_MAILBOX_INT3

RW1C

Set to 1 when the

A2P_MAILBOX3

is written to.

20

A2P_MAILBOX_INT4

RW1C

Set to 1 when the

A2P_MAILBOX4

is written to.

21

A2P_MAILBOX_INT5

RW1C

Set to 1 when the

A2P_MAILBOX5

is written to.

22

A2P_MAILBOX_INT6

RW1C

Set to 1 when the

A2P_MAILBOX6

is written to.

23

A2P_MAILBOX_INT7

RW1C

Set to 1 when the

A2P_MAILBOX7

is written to.

31:24

Reserved

N/A

Table 7–18. PCI Interrupt Status Register – Address: 0x0040 (Part 2 of 2)

Bit

Name

Access

Mode

Description