Bit single-cycle memory write master transactions, Burst memory, Figure 3–42 – Altera PCI Compiler User Manual

Page 193

Altera Corporation

User Guide Version 11.1

3–119

October 2011

Functional Description

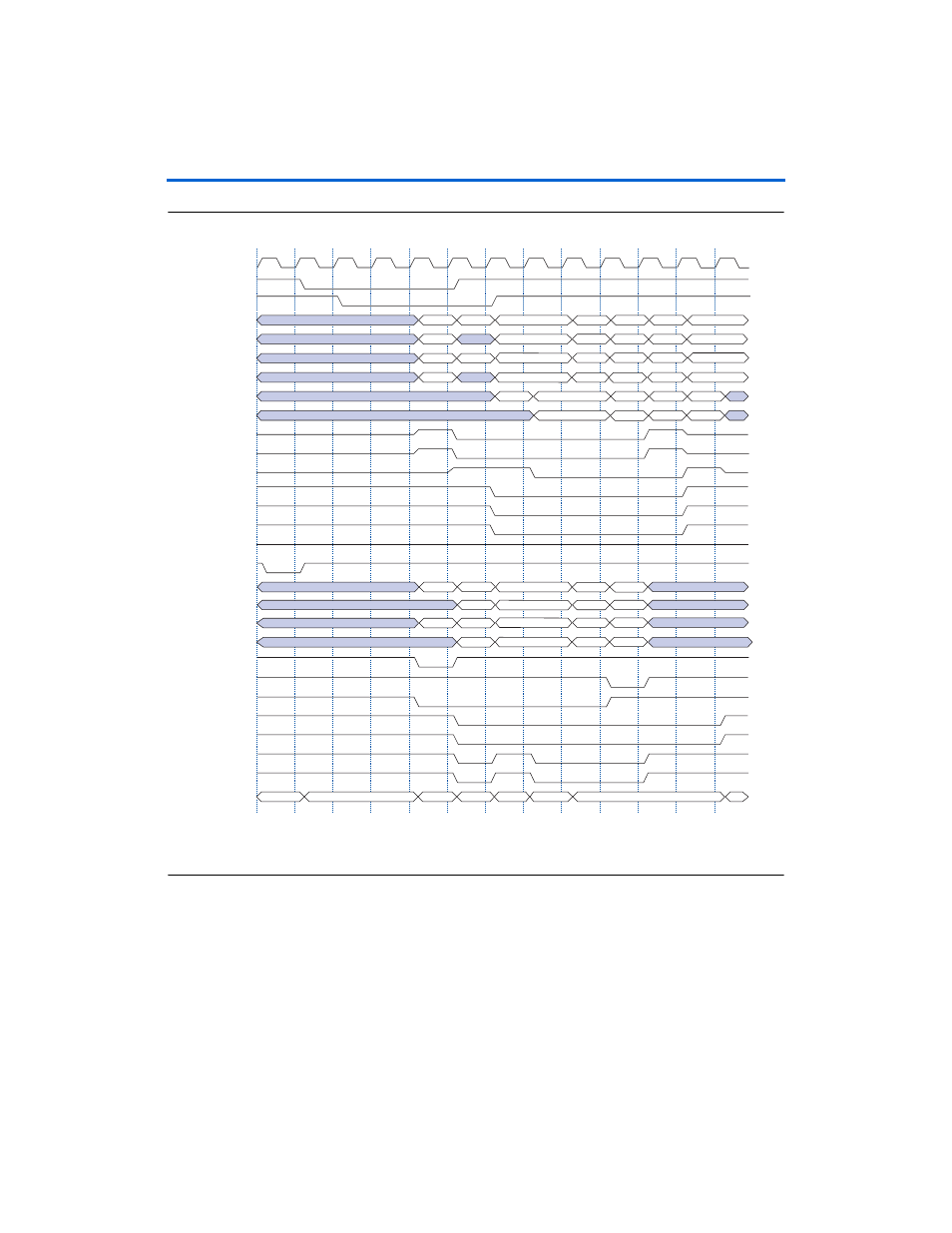

Figure 3–42. Burst Memory Write Master Transaction with Variable Byte Enables

Notes to

:

(1)

This signal is not applicable to the pci_mt32 MegaCore function.

(2)

For pci_mt32, lm_req32n should be substituted for lm_req64n for 32-bit master transactions.

32-Bit Single-Cycle Memory Write Master Transactions

shows a 32-bit single-cycle memory write master transaction.

The transaction shown in

is the same as that shown in

, except that the local side master interface transfers only one

data word. This figure applies to both the pci_mt64 and pci_mt32

MegaCore functions, excluding the 64-bit extension signals as noted for

pci_mt32

.

2

3

4

5

6

7

9

10

12

clk

reqn

8

11

1

gntn

ad[31..0]

(1) ad[63..32]

cben[3..0]

(1) cben[7..4]

par

(1) par64

framen

(1) req64n

irdyn

devseln

(1) ack64n

trdyn

stopn

Adr

7

Adr-PAR

D0_L

0

0

0

0

D2_L

D3_L

13

l_adi[31..0]

Adr

7

(1) l_adi[63..32]

D0_H

D0_L

D3_H

D3_L

D1_L

D1_H

l_cbeni[3..0]

BE0_L

(1) l_cbeni[7..4]

BE0_H

(1), (2) lm_req64n

lm_lastn

lm_adr_ackn

lm_rdyn

lm_tsr[9..0]

000

001

004

002

308

008

208

000

(1) l_ldat_ackn

(1) l_hdat_ackn

lm_ackn

lm_dxfrn

D0_H

Z

D2_H

D3_H

D0-L-PAR

D2-L-PAR

D3-L-PAR

D0-H-PAR

D2-H-PAR

D3-H-PAR

Z

Z

D1_L

D1_H

D1-L-PAR

D1-H-PAR

D2_L

D2_H

BE1_L

BE2_L

BE0_L

BE1_L

BE3_L

BE0_H

BE1_H

BE3_H

BE3_H

Z

BE2_L

BE3_L

BE1_H

BE2_H

BE3_H