Control register access avalon slave, Figure 7–4, Pci host-bridge device mode – Altera PCI Compiler User Manual

Page 277

Altera Corporation

User Guide Version 11.1

7–9

October 2011

Functional Description

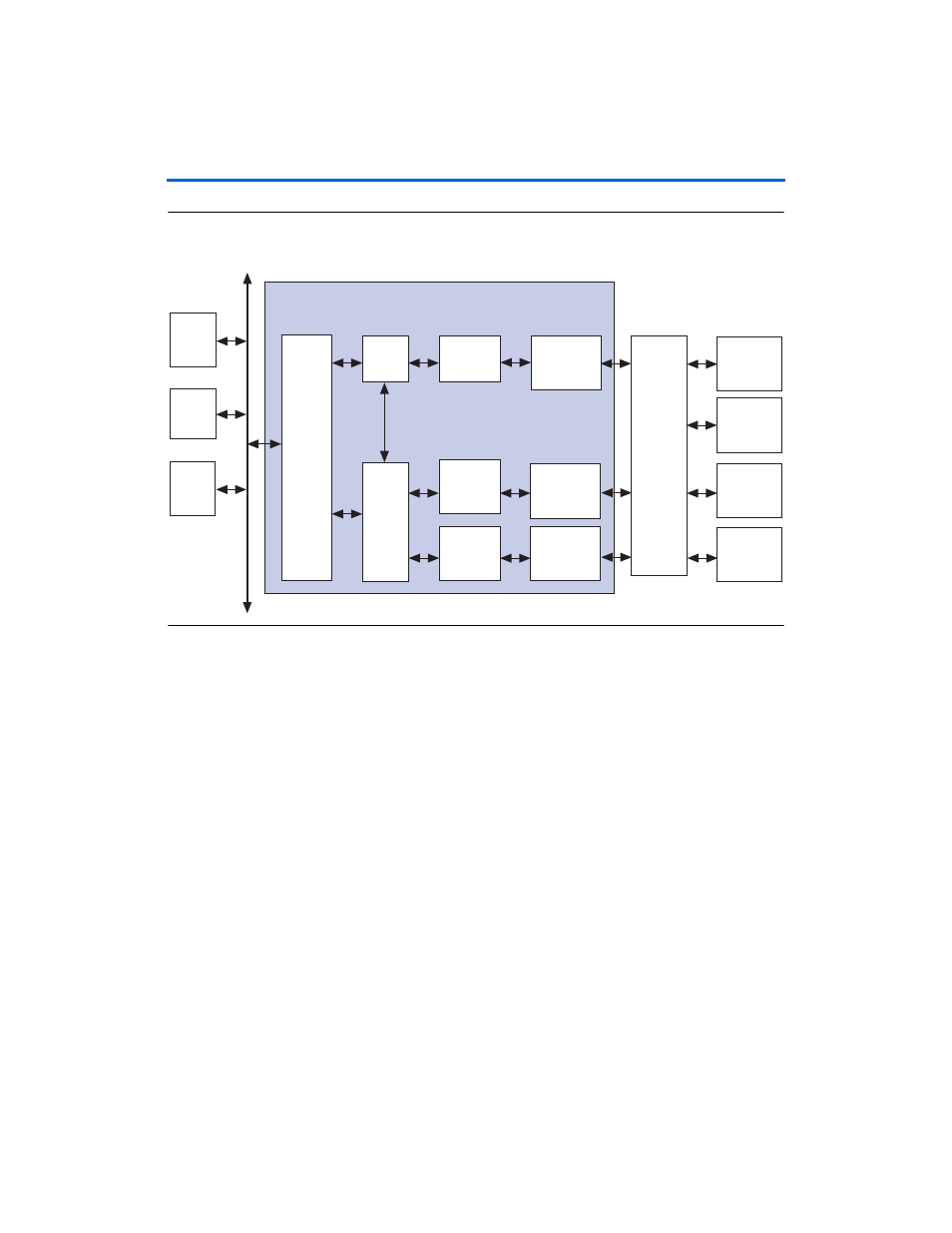

Figure 7–4. PCI-Avalon Bridge Block Diagram Managing the PCI Master/Target Peripheral Mode

You can customize the Master/Target mode by specifying one of the

performance profiles. Refer to

“Performance Profiles” on page 7–11

.

Control Register Access Avalon Slave

The PCI-Avalon bridge provides a rich set of user-accessible

control/status registers. Implementing the registers is optional except

when using the:

■

PCI Host-Bridge Device mode

■

Dynamic Avalon-to-PCI address translation option

The Avalon Configuration tab of the PCI Compiler wizard allows you to

enable the control/status registers and specify access to them via the

interconnect. Refer to

“Avalon Configuration” on page 6–16

.

The control/status registers can be accessed from any Avalon-MM

master device including PCI-Avalon bridge master ports. If you want to

access the control/status registers from a PCI bus master device, you

must use the SOPC Builder GUI to connect the Avalon-MM ports to the

Control Register Access Avalon Slave

port. Refer to

.

PCI-Avalon Bridge

Master/Target Peripheral Mode

PCI

MegaCore

Function

PCI

Target

Controller

Non-

Prefetchable

Avalon

Master

Host

Processor

PCI

Master/

Target

Device

PCI

Bus

Arbiter

Prefetchable

Avalon

Master

PCI

Prefetchable

Bridge

Logic

PCI

Non-

Prefetchable

Bridge Logic

PCI

Bus

PCI

Master

Controller

Master

Bridge

Logic

PCI Bus

Access

Avalon Slave

Master

Peripheral

Master

Peripheral

Slave

Peripheral

Slave

Peripheral

System

Interconnect

Fabric