Ieee 1588v2 feature pma delay, Ieee 1588v2 feature pma delay -17 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 100

HW Reset

Description

R/W

Name

Dword

Offset

0x0

Static timing adjustment in fractional

nanoseconds for outbound timestamps on the

receive datapath.

• Bits 0 to 15: Timing adjustment in fractional

nanoseconds.

• Bits 16 to 31: Not used.

RW

rx_adjust_fns

0xD4

0x0

Static timing adjustment in nanoseconds for

outbound timestamps on the receive datapath.

• Bits 0 to 15: Timing adjustment in nanosec-

onds.

• Bits 16 to 23: Not used.

RW

rx_adjust_ns

0xD5

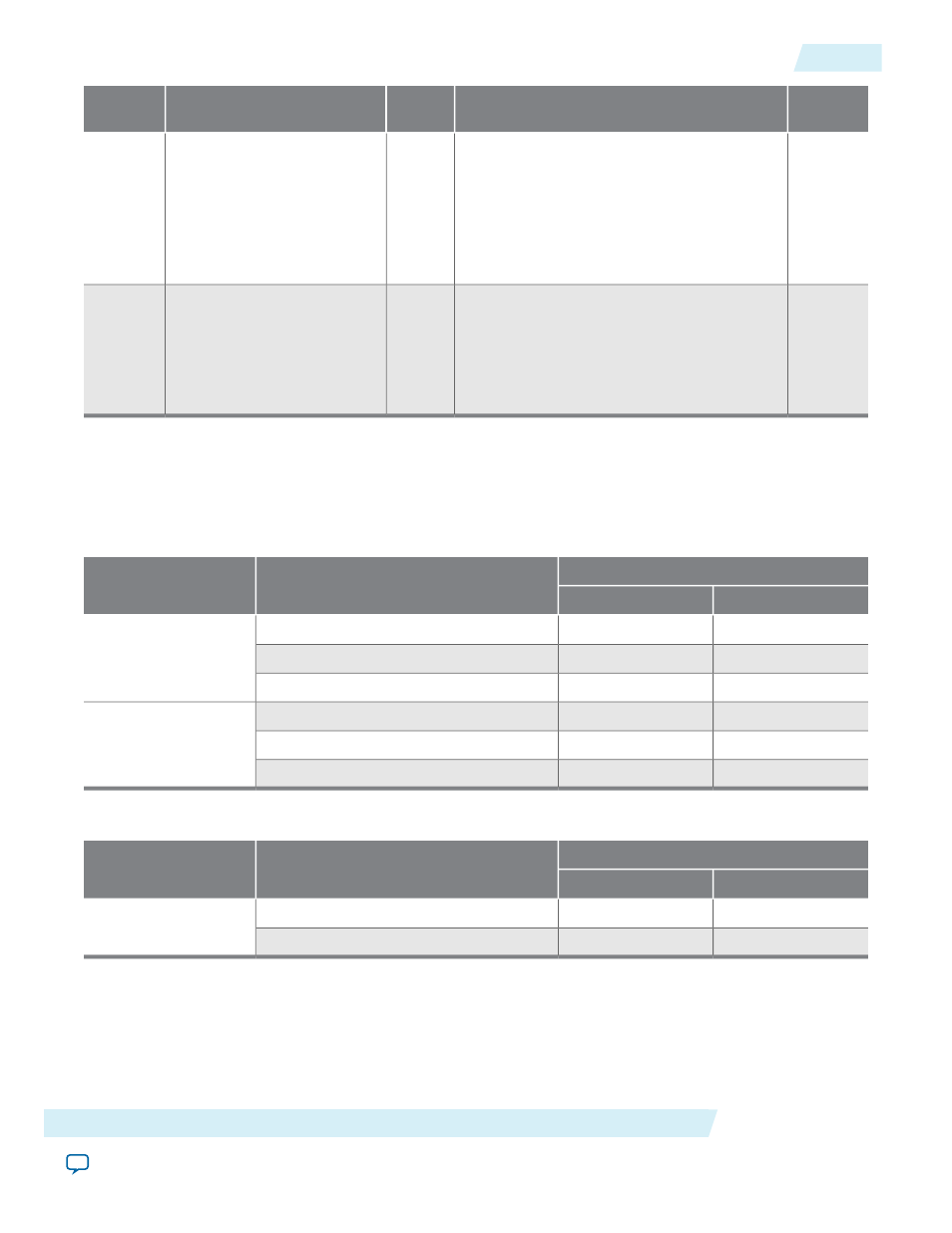

IEEE 1588v2 Feature PMA Delay

PMA digital and analog delay of hardware for the IEEE 1588v2 feature and the register timing adjustment.

1 UI is equivalent to 800 ps.

Table 6-8: IEEE 1588v2 Feature PMA Delay—Hardware

Timing Adjustment

Device

Delay

RX register

TX register

26 UI

53 UI

Stratix V or Arria V GZ

Digital

34 UI

52 UI

Arria V GX, Arria V GT, or Arria V SoC

44 UI

32 UI

Cyclone V GX or Cyclone V SoC

1.75 ns

-1.1 ns

Stratix V

Analog

1.75 ns

-1.1 ns

Arria V

1.75 ns

-1.1 ns

Cyclone V

Table 6-9: IEEE 1588v2 Feature LVDS I/O Delay—Hardware

Timing Adjustment

Device

Delay

RX register

TX register

36 UI

11 UI

Stratix V or Arria V GZ

Digital

36 UI

11 UI

Arria V GX, Arria V GT, or Arria V SoC

PMA digital and analog delay of simulation model for the IEEE 1588v2 feature and the register timing

adjustment.

Altera Corporation

Configuration Register Space

6-17

IEEE 1588v2 Feature PMA Delay

UG-01008

2014.06.30