Generated files, Generated files -9 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 28

Generated Files

The type of files generated in your project directory and their names may vary depending on the custom

variation of the MegaCore function you created.

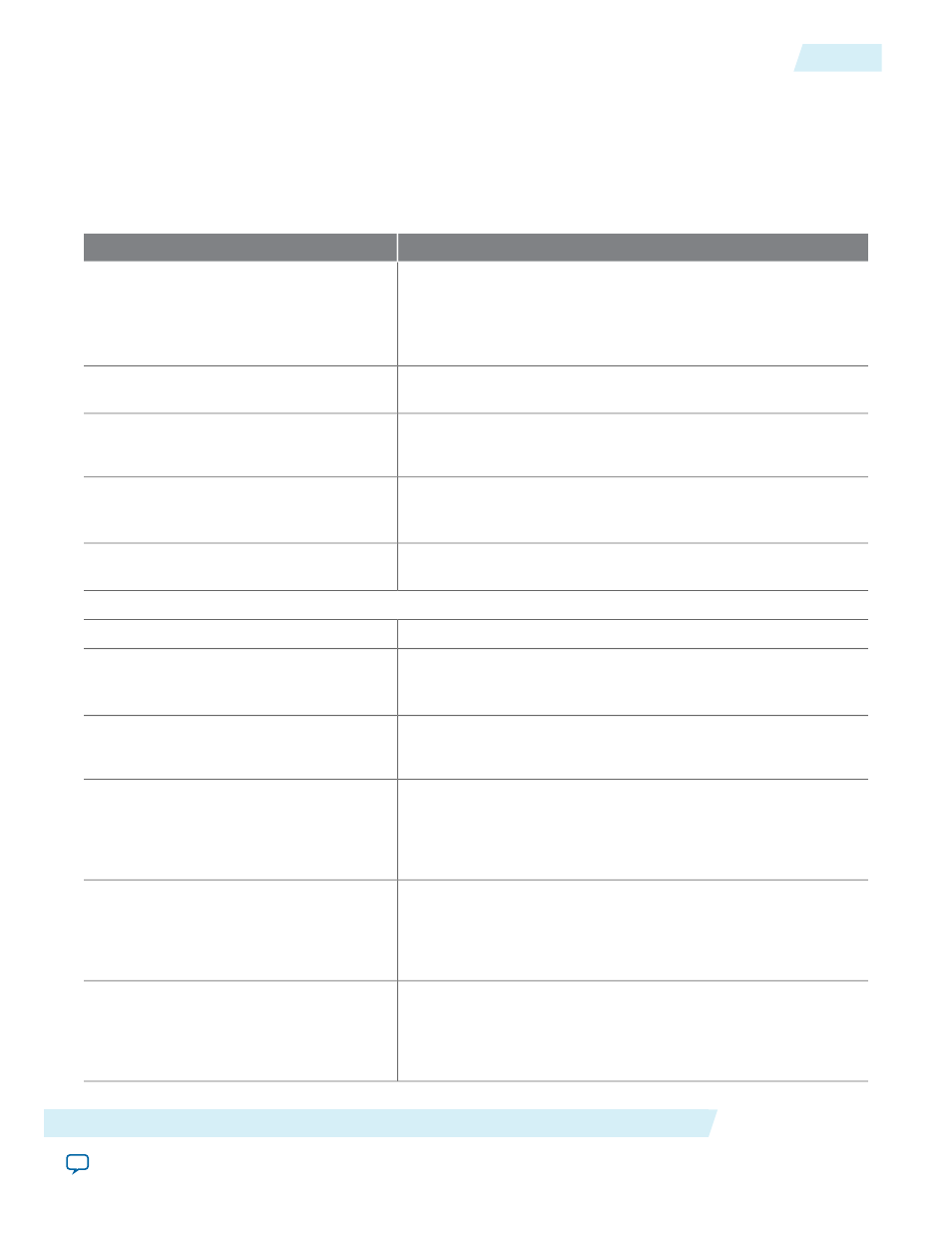

Table 2-1: Generated Files

Description

File Name

A MegaCore function variation file, which defines a VHDL or

Verilog HDL top-level description of the custom MegaCore

function. Instantiate the entity defined by this file inside your

design. Include this file when compiling your design in the

Quartus II software.

<variation_name>

.v

or

<variation_name>

.vhd

Quartus II symbol file for the MegaCore function variation. You

can use this file in the Quartus II block diagram editor.

<variation_name>

.bsf

Contains Quartus II project information for your MegaCore

function variations.

<variation_name>

.qip

and

<variation_name>.sip

A VHDL component declaration file for the MegaCore function

variation. Add the contents of this file to any VHDL architecture

that instantiates the MegaCore.

<variation_name>

.cmp

Simulation Package Descriptor file. Specifies the files required

for simulation.

<variation_name>

.spd

Testbench Files (in <variation_name>_testbench folder)

Read me file for the testbench design.

README.txt

Dummy Quartus II project and project setting file. Use this to

start the Quartus II in the correct directory to launch the

generate_

sim_verilog.tcl

and

generate_sim_vhdl.tcl

files.

generate_sim.qpf and

generate_sim.qsf

A Tcl script to generate the DUT VHDL or Verilog HDL

simulation model for use in the testbench.

generate_sim_verilog.tcl and

generate_sim_vhdl.tcl

VHDL or Verilog HDL testbench that exercises your MegaCore

function variation in a third party simulator.

/testbench_vhdl/<variation_name>/

<variation_name>_tb.vhd or

/testbench_verilog/<variation_name>/

<variation_name>_tb.v

A Tcl script for use with the ModelSim simulation software.

/testbench_vhdl/<variation_name>/run_

<variation_name>_tb.tcl or

/testbench_verilog/<variation_name>/

run_ <variation_name>_tb.tcl

A signal tracing macro script used with the ModelSim simulation

software to display testbench signals.

/testbench_vhdl/<variation_name>/

<variation_name>_wave.do or

/testbench_verilog/<variation_name>/

<variation_name>_wave.do

Altera Corporation

Getting Started with Altera IP Cores

2-9

Generated Files

UG-01008

2014.06.30