Fifo buffer thresholds, Fifo buffer thresholds -12 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 48

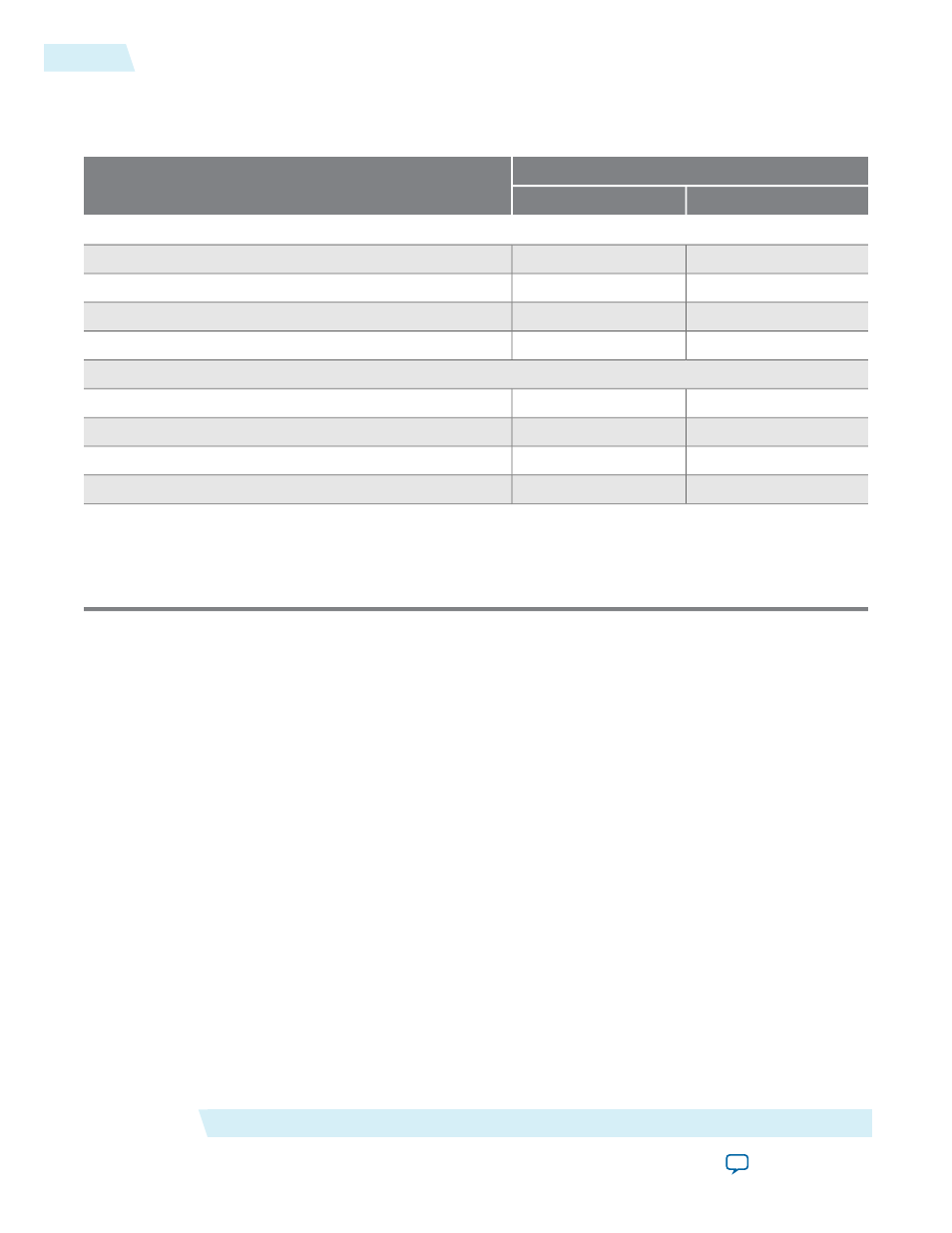

Table 4-5: Transmit and Receive Nominal Latency

The transmit and receive nominal latencies in various modes. The FIFO buffer thresholds are set to the typical values

specified in this user guide when deriving the latencies.

Latency (Clock Cycles)

MAC Configuration

Receive

Transmit

MAC with Internal FIFO Buffers

110

32

GMII in cut-through mode

218

41

MII in cut-through mode

113

33

RGMII in gigabit and cut-through mode

221

42

RGMII in 10/100 Mbps and cut-through mode

MAC without Internal FIFO Buffers

37

11

GMII

77

22

MII

40

12

RGMII in gigabit mode

80

23

RGMII in10/100 Mbps

Notes to

:

1. The clocks in all domains are running at the same frequency.

2. The data width is set to 32 bits.

3. The data width is set to 8 bits.

Related Information

Base Configuration Registers (Dword Offset 0x00 – 0x17)

on page 6-3

FIFO Buffer Thresholds

For MAC variations with internal FIFO buffers, you can change the operations of the FIFO buffers, and

manage potential FIFO buffer overflow or underflow by configuring the following thresholds:

• Almost empty

• Almost full

• Section empty

• Section full

These thresholds are defined in bytes for 8-bit wide FIFO buffers and in words for 32-bit wide FIFO buffers.

The FIFO buffer thresholds are configured via the registers.

Functional Description

Altera Corporation

UG-01008

FIFO Buffer Thresholds

4-12

2014.06.30