Altera Triple Speed Ethernet MegaCore Function User Manual

Page 221

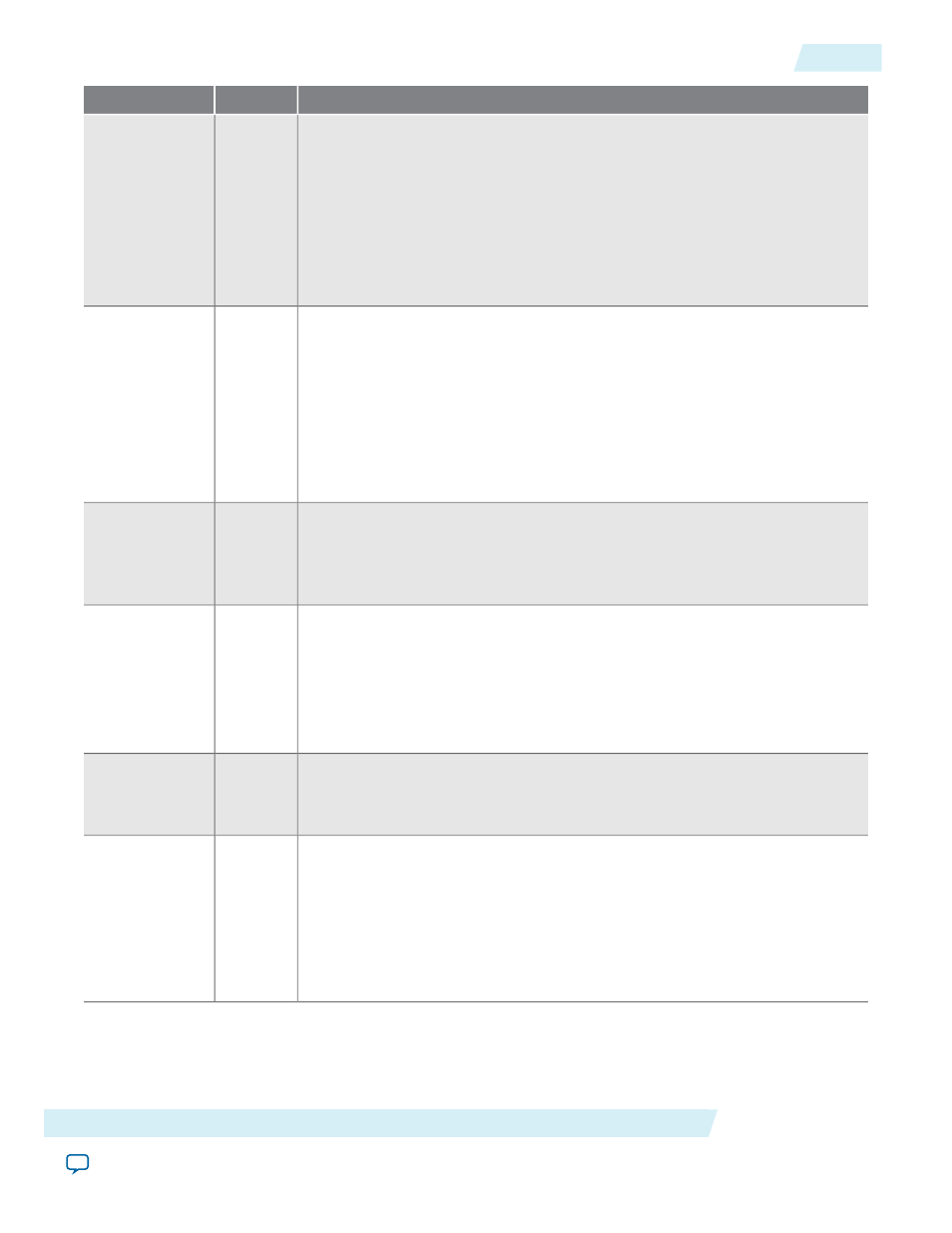

Changes

Version

Date

• Added Altera IEEE 1588v2 Feature section in Chapter 4.

• Added information for the following GUI parameters: Enable timestamping,

Enable PTP 1-step clock, and Timestamp fingerprint width in “Timestamp

Options”.

• Added MAC registers with IEEE 1588v2 feature.

• Added IEEE 1588v2 feature signals tables.

• Added Triple-Speed Ethernet with IEEE 1588v2 Design Example section.

• Added Time-of-Day Clock section.

12.1

January 2013

• Added support for Cyclone V.

• Updated the Congestion and Flow Control section in Chapter 4.

• Added Register Initialization section in Chapter 5.

• Added

holdoff_quant

register description.

• Added

UNIDIRECTIONAL_ENABLE

bit description.

• Revised and moved the section on Timing Constraint to a new chapter.

• Added information about how to customize the SDC file in Chapter 8.

• Added Pause Frame Generation section.

12.0

June 2012

• Added support for Arria V.

• Revised the Device Family Support section in Chapter 1.

• Added

disable_read_timeout

and

read_timeout

registers at address 0x15

and 0x16.

11.1

November

2011

• Updated support for Cyclone IV GX, Cyclone III LS, Aria II GZ,

HardCopy IV GX/E and HardCopy III E devices.

• Revised Performance and Resource Utilization section in Chapter 1.

• Updated Chapter 3 to include Qsys System Integration Tool Design Flow.

• Added Transmit and Receive Latencies section in Chapter 4.

• Updated all MAC register address to dbyte addressing.

11.0

June 2011

• Added support for Arria II GZ.

• Added a new parameter, Starting Channel Number.

• Streamlined the contents and document organization.

10.1

December

2010

• Added support for Stratix V.

• Revised the nomenclature of device support types.

• Added chapter 5, Design Considerations. Moved the Clock Distribution

section to this chapter and renamed it to Optimizing Clock Resources in

Multiport MAC and PCS with Embedded PMA. Added sections on PLL

Sharing and Transceiver Quad Sharing.

• Updated the description of Enable transceiver dynamic reconfiguration.

10.0

August 2010

Altera Corporation

Additional Information

F-5

Document Revision History

UG-01008

2014.06.30