Altera Triple Speed Ethernet MegaCore Function User Manual

Page 143

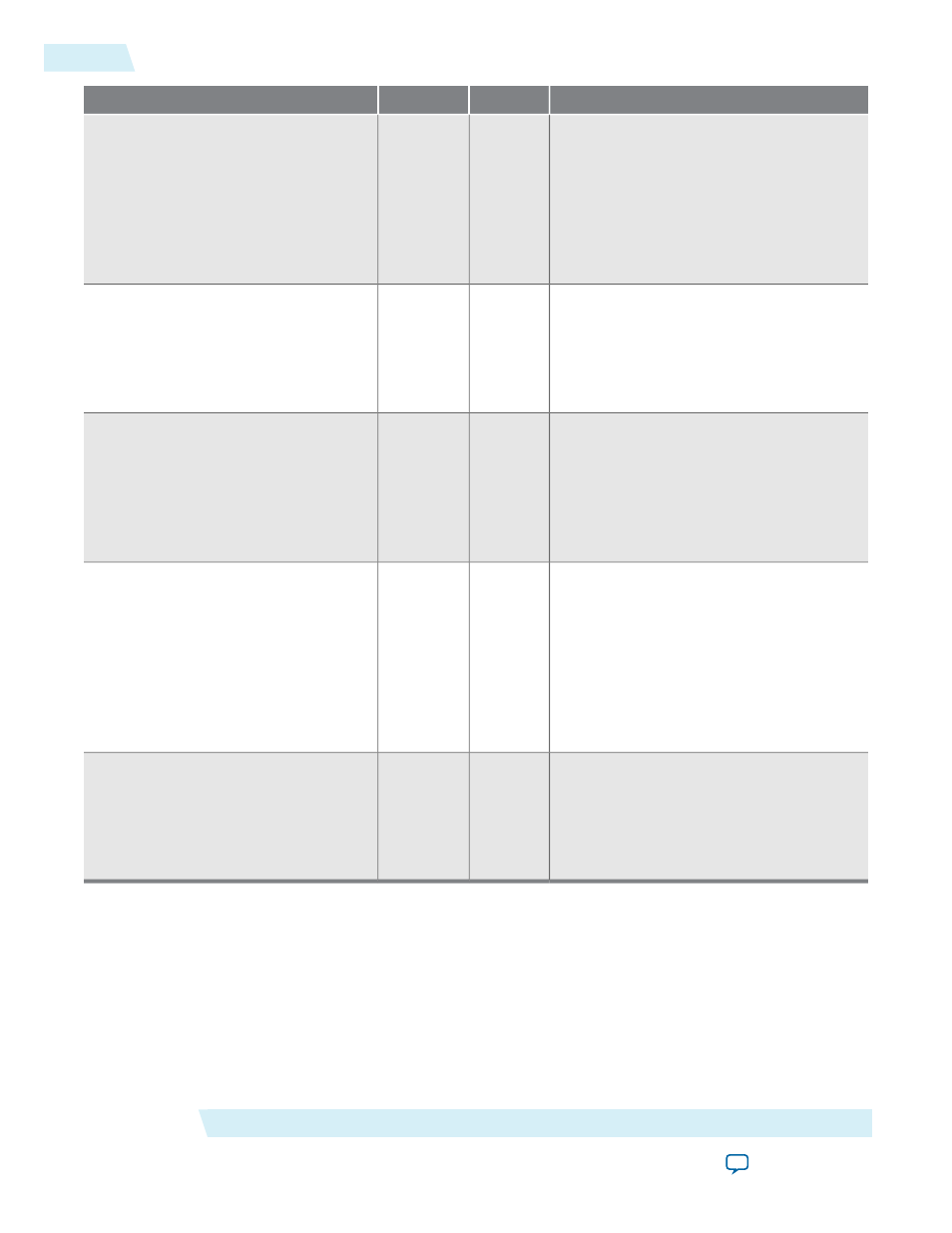

Description

Width

I/O

Signal

A transmit interface signal. Assert this

signal to indicate that a timestamp is

obtained and a timestamp request is valid

for the particular frame.

Assert this signal in the same clock cycle

as the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

O

tx_egress_timestamp_96b_valid

Configurable width fingerprint that returns

with correlated timestamps.

The signal width is determined by the

TSTAMP_FP_WIDTH parameter (default

parameter value is 4).

n

O

tx_egress_timestamp_96b_

fingerprint

A transmit interface signal. This signal

requests timestamp of frames on the TX

path. The timestamp is used to calculate

the residence time.

Consists of 48-bit nanoseconds field and

16-bit fractional nanoseconds field.

64

O

tx_egress_timestamp_64b_data

A transmit interface signal. Assert this

signal to indicate that a timestamp is

obtained and a timestamp request is valid

for the particular frame.

Assert this signal in the same clock cycle

as the start of packet (

avalon_st_tx_

startofpacket

or

avalon_st_tx_

startofpacket_n

is asserted).

1

O

tx_egress_timestamp_64b_valid

Configurable width fingerprint that returns

with correlated timestamps.

The signal width is determined by the

TSTAMP_FP_WIDTH parameter (default

parameter value is 4).

n

O

tx_egress_timestamp_64b_

fingerprint

Interface Signals

Altera Corporation

UG-01008

IEEE 1588v2 TX Timestamp Signals

7-28

2014.06.30