Altera Triple Speed Ethernet MegaCore Function User Manual

Page 146

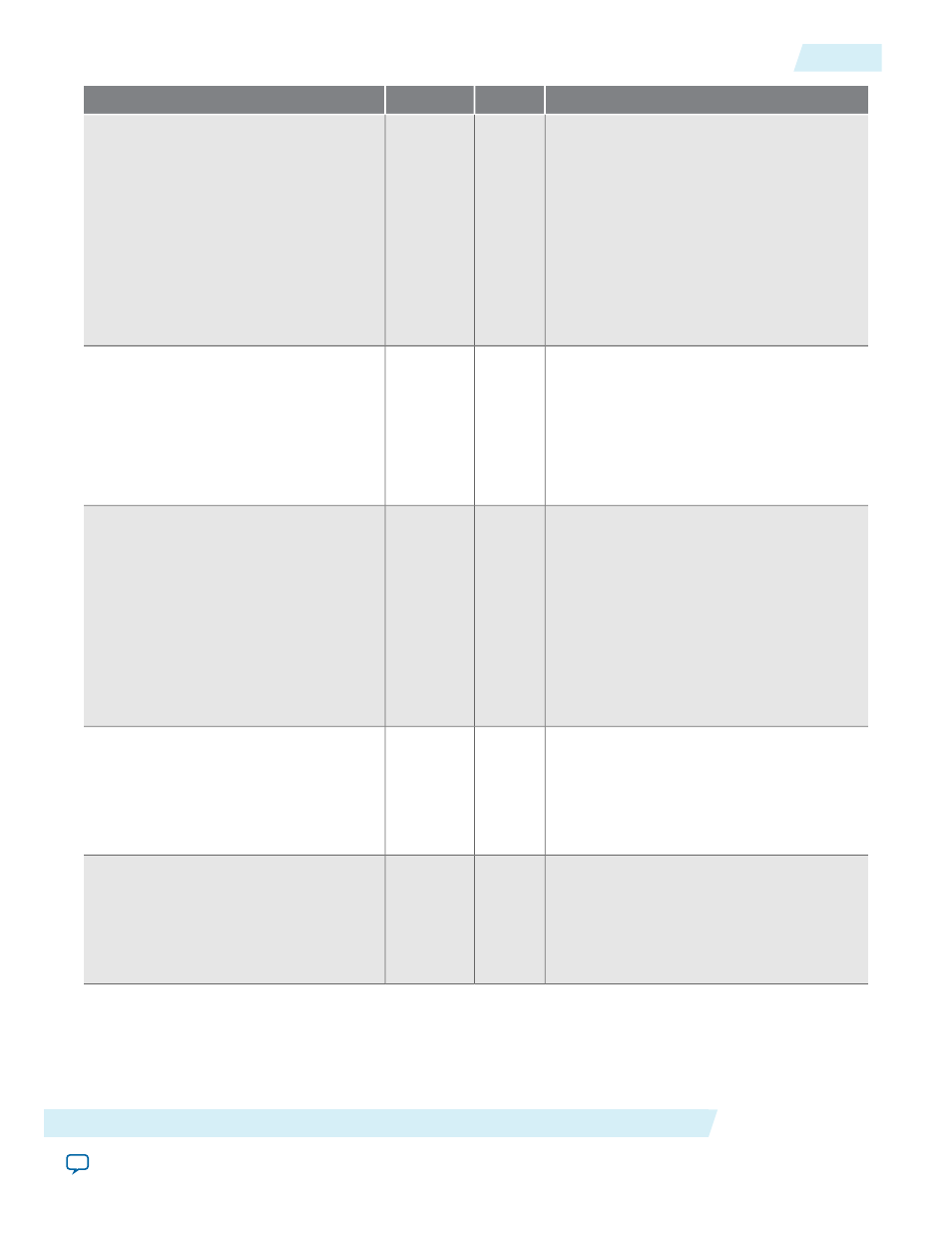

Description

Width

I/O

Signal

Format of timestamp to be used for

residence time calculation.

0: 96-bits (96-bits egress timestamp - 96-

bits ingress timestamp).

1: 64-bits (64-bits egress timestamp - 64-

bits ingress timestamp).

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

I

tx_etstamp_ins_ctrl_residence_

time_calc_format

Assert this signal to set the checksum field

of UDP/IPv4 to zero.

Required offset location of checksum field.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

I

tx_etstamp_ins_ctrl_checksum_zero

Assert this signal to correct UDP/IPv6

packet checksum, by updating the

checksum correction, which is specified by

checksum correction offset.

Required offset location of checksum

correction.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

I

tx_etstamp_ins_ctrl_checksum_

correct

The location of the timestamp field, relative

to the first byte of the packet.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

I

tx_etstamp_ins_ctrl_offset_

timestamp

The location of the correction field, relative

to the first byte of the packet.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

16

I

tx_etstamp_ins_ctrl_offset_

correction_field[]

Altera Corporation

Interface Signals

7-31

IEEE 1588v2 TX Insert Control Timestamp Signals

UG-01008

2014.06.30