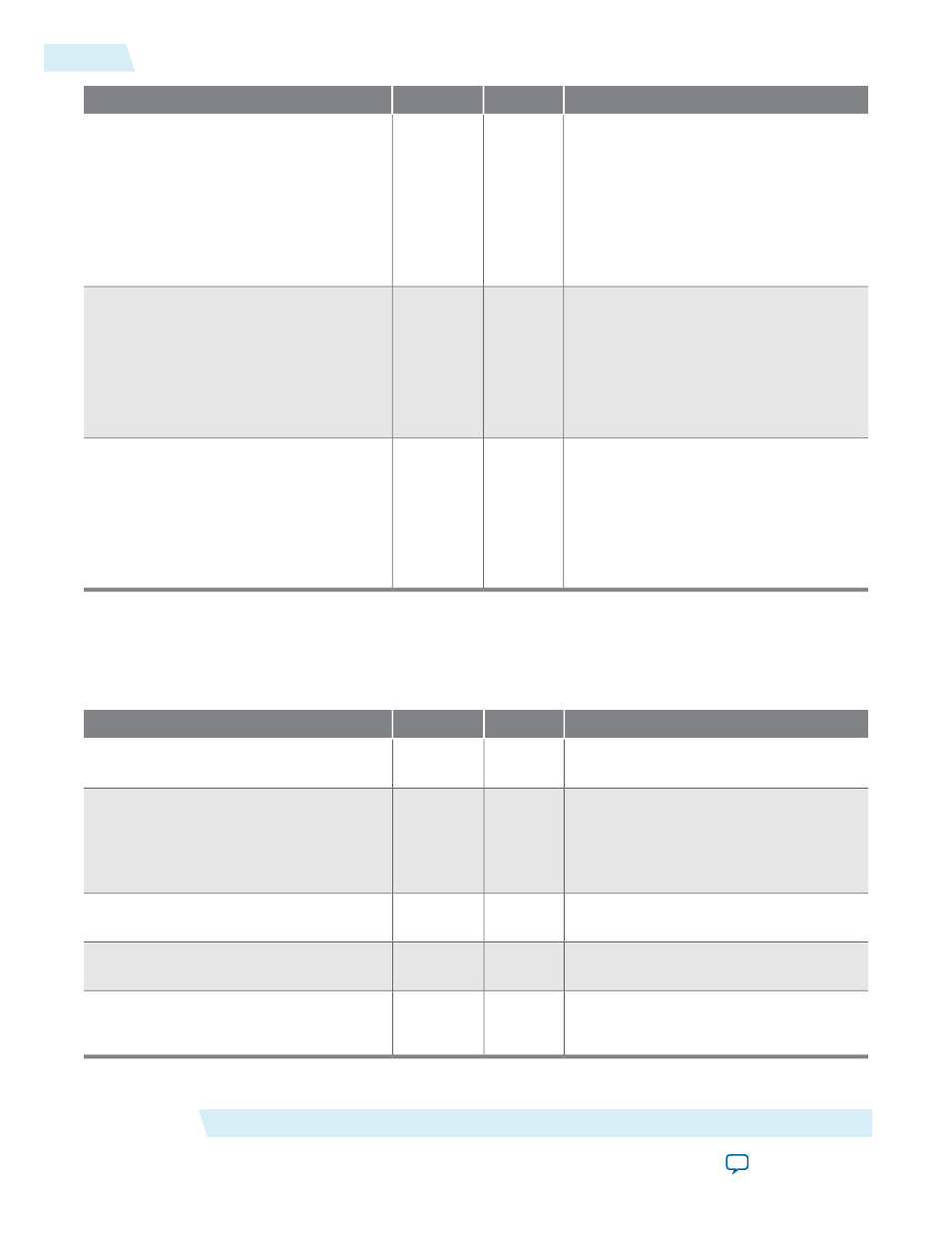

Packet classifier control insert signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 215

Description

Width

Direction

Signal

Indicates the update for residence time.

• 1: Allows update for residence time

based on decoded results.

• 0: Prevents update for residence time.

When this signal is deasserted,

tx_

etstamp_ins_ctrl_out_residence_

time_update

also gets deasserted.

1

Input

tx_etstamp_ins_ctrl_in_residence_

time_update

Format of the timestamp to be used for

calculating residence time. This signal

must be aligned to the start of an

incoming packet.

• 1: 64-bit timestamp format

• 0: 96-bit timestamp format

1

Input

tx_etstamp_ins_ctrl_in_residence_

time_calc_format

Format of the timestamp to be used for

calculating residence time. This signal

must be aligned to the start of an

outgoing packet.

• 1: 64-bit timestamp format

• 0: 96-bit timestamp format

1

Output

tx_etstamp_ins_ctrl_out_residence_

time_calc_format

Packet Classifier Control Insert Signals

These signals must be aligned to the start of a packet.

Table E-5: Control Insert Signals for the Packet Classifier

Description

Width

Direction

Signal

Assert this signal to set the checksum

field.

1

Output

tx_etstamp_ins_ctrl_out_checksum_

zero

Assert this signal to correct the packet

checksum by updating the checksum

correction specified by

tx_etstamp_

ins_ctrl_out_offset_checksum_

correction

.

1

Output

tx_etstamp_ins_ctrl_out_checksum_

correct

The timestamp format of the frame

where the timestamp is inserted.

1

Output

tx_etstamp_ins_ctrl_out_timestamp_

format

Assert this signal to insert timestamp

into the associated frame.

1

Output

tx_etstamp_ins_ctrl_out_timestamp_

insert

Assert this signal to add the residence

time into the correction field of the PTP

frame.

1

Output

tx_etstamp_ins_ctrl_out_residence_

time_update

Packet Classifier

Altera Corporation

UG-01008

Packet Classifier Control Insert Signals

E-4

2014.06.30