Design constraint file no longer generated, Design constraint file no longer generated -10 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 29

Description

File Name

A directory containing VHDL and Verilog HDL models of the

Ethernet generators and monitors used by the generated testbench.

/testbench_vhdl/models or

/testbench_verilog/models

Design Constraint File No Longer Generated

For a new Triple-Speed Ethernet MegaCore function created using the Quartus II software ACDS 13.0 or

later, the Quartus II software no longer generate the <variation_name>

_constraints.tcl

file that contains the

necessary constraints for the compilation of your MegaCore Function variation.

lists the

recommended Quartus II pin assignments that you can set in your design.

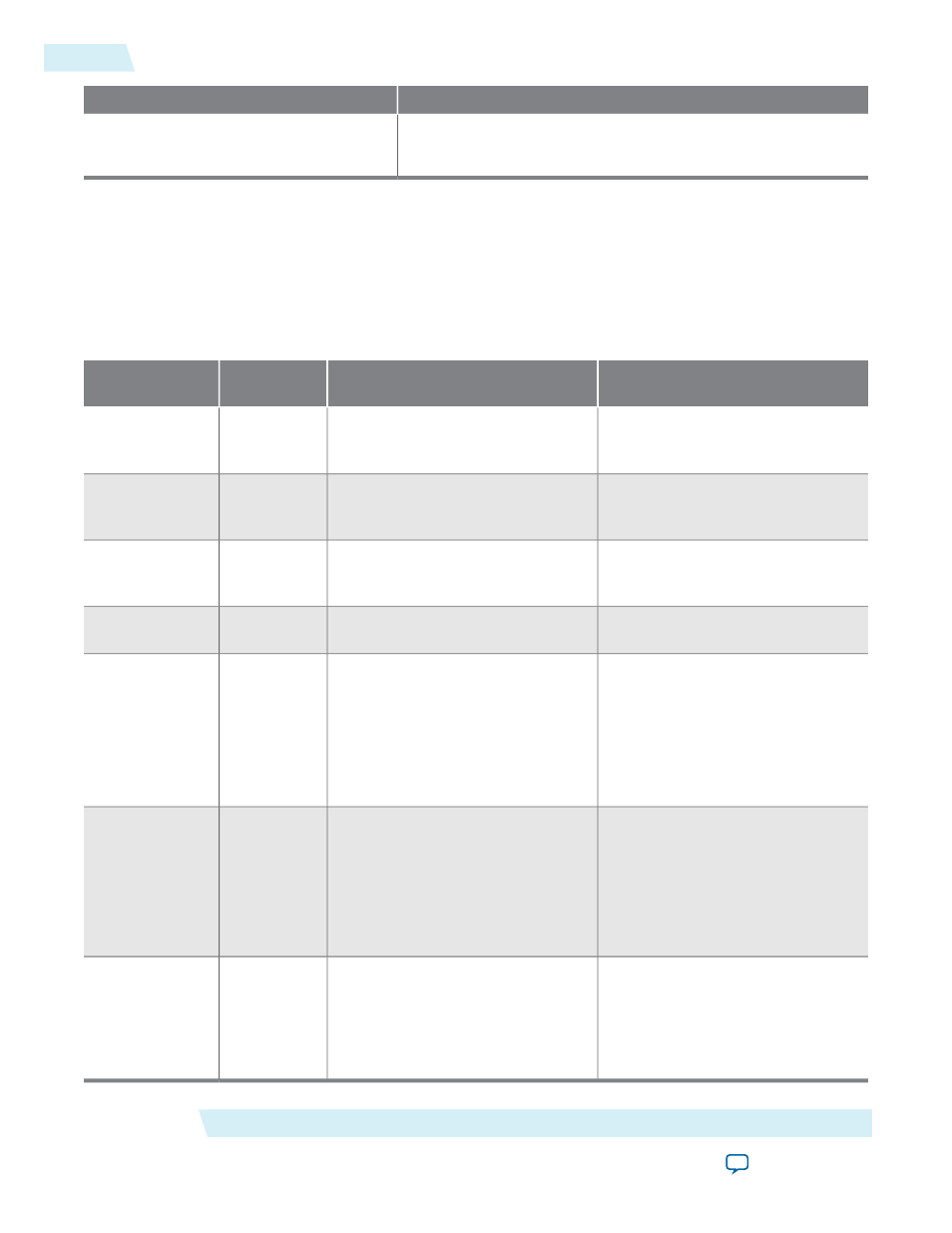

Table 2-2: Recommended Quartus II Pin Assignments

Design Pin

Description

Assignment

Value

Quartus II Pin

Assignment

MII, GMII, RGMII, TBI input pins.

To optimize I/O timing for MII, GMII

and TBI interface.

ON

FAST_

INPUT_

REGISTER

MII, GMII, RGMII, TBI output

pins.

To optimize I/O timing for MII, GMII

and TBI interface.

ON

FAST_

OUTPUT_

REGISTER

GXB transceiver serial input and

output pins.

I/O standard for GXB serial input and

output pins.

1.4-V PCML

or 1.5-V

PCML

IO_

STANDARD

LVDS/IO transceiver serial input

and output pins.

I/O standard for LVDS/IO serial input

and output pins.

LVDS

IO_

STANDARD

•

ref_clk

for MAC and PCS with

LVDS/IO (with internal FIFO).

•

clk

and

reset

pins for MAC

only (without internal FIFO).

•

clk

and

ref_clk

input pins for

MAC and PCS with transceiver

(without internal FIFO).

To assign clock signals to use the global

clock network. Use this setting to guide

the Quartus II in the fitter process for

better timing closure.

Global clock

GLOBAL_

SIGNAL

•

rx_clk <n>

and

tx_clk <n>

input pins for MAC only using

MII/GMII interface (without

internal FIFO).

•

rx_clk <n>

input pin for MAC

only using RGMII interface

(without internal FIFO).

To assign clock signals to use the

regional clock network. Use this setting

to guide the Quartus II in the fitter

process for better timing closure.

Regional clock

GLOBAL_

SIGNAL

Signals for Arria V devices:

•

*reset_ff_wr

and

*reset_ff_

rd

•

*| altera_tse_reset_

synchronizer_chain_out

To prevent a signal to be used as a

global signal.

OFF

GLOBAL_

SIGNAL

Getting Started with Altera IP Cores

Altera Corporation

UG-01008

Design Constraint File No Longer Generated

2-10

2014.06.30