Altera Triple Speed Ethernet MegaCore Function User Manual

Page 111

Triple-Speed Ethernet System with MII/GMII or RGMII

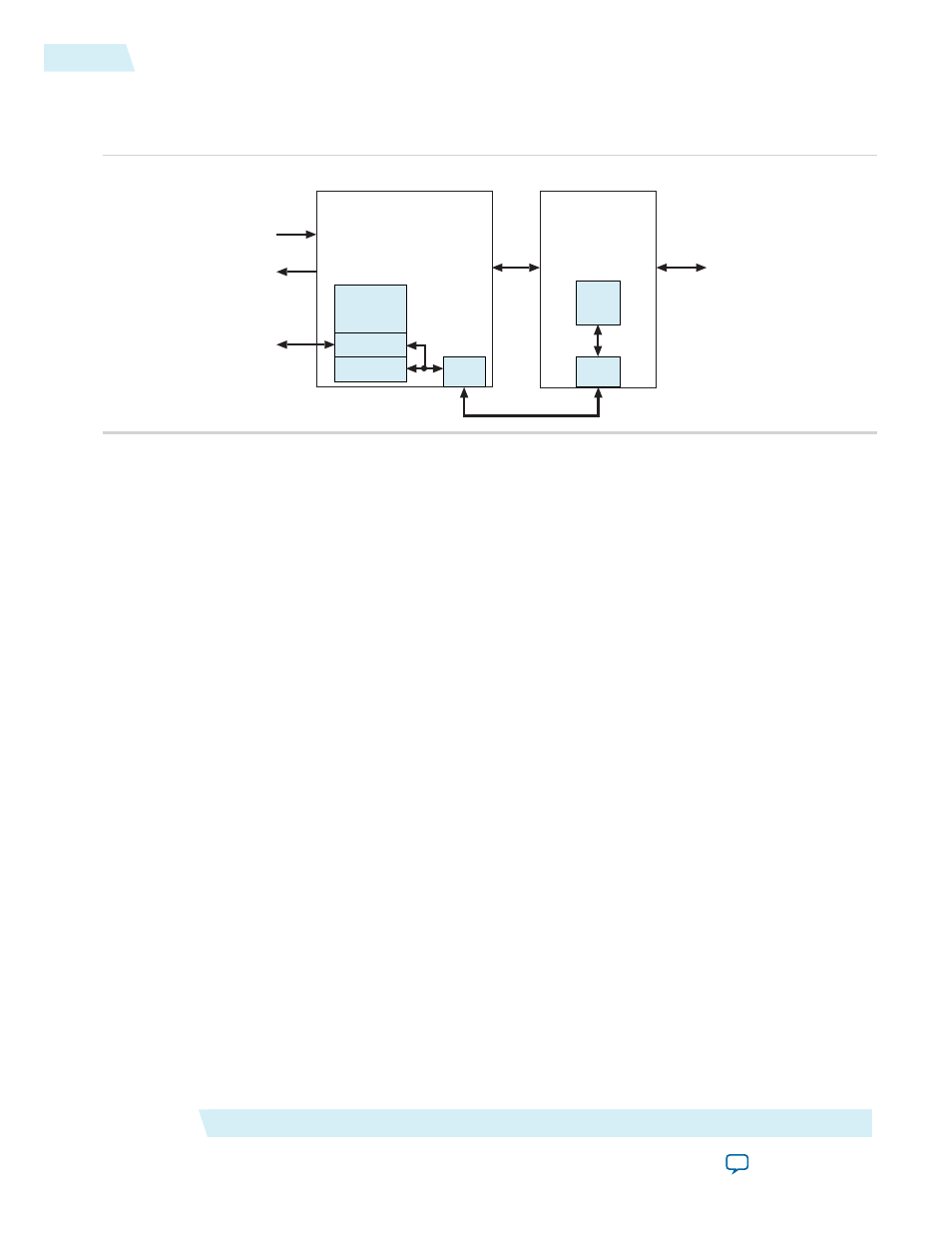

Figure 6-2: Triple-Speed Ethernet System with MII/GMII or RGMII with Register Initialization Recommendation

10/100/1000 Mbps MAC

External PHY

MAC

Register

Space

MDIO Space 0

MDIO Space 1

MDIO

Host

PHY

Register

Space

MDIO

Slave

Avalon ST TX

Avalon ST RX

Avalon MM

Copper/Fiber

Interface

MII/GMII/RGMII Interface

MDIO

Use the following recommended initialization sequences for the example in

.

1. External PHY Initialization using MDIO

//Assume the External PHY Address is 0x0A

mdio_addr0 = 0x0A

//External PHY Register will Map to MDIO Space 0

Read/write to MDIO space 0 (dword offset 0x80 - 0x9F) = Read/write to PHY Register 0 to 31

2. MAC Configuration Register Initialization

a. Disable MAC Transmit and Receive DatapathDisable the MAC transmit and receive datapath before

performing any changes to configuration.

//Set TX_ENA and RX_ENA bit to 0 in Command Config Register

Command_config Register = 0x00802220

//Read the TX_ENA and RX_ENA bit is set 0 to ensure TX and RX path is disable

Wait Command_config Register = 0x00802220

b. MAC FIFO Configuration

Tx_section_empty = Max FIFO size - 16

Tx_almost_full = 3

Tx_almost_empty = 8

Rx_section_empty = Max FIFO size - 16

Rx_almost_full = 8

Rx_almost_empty = 8

//Cut Throught Mode, Set this Threshold to 0 to enable Store and Forward Mode

Configuration Register Space

Altera Corporation

UG-01008

Triple-Speed Ethernet System with MII/GMII or RGMII

6-28

2014.06.30