Phy loopback, Phy power-down, Phy loopback -33 phy power-down -33 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 69

Figure 4-19: SERDES Serialization Overview

serialization

tbi_tx_d(9:0)

1.25Gbps

Serial Stream

9

0

On receive, the SERDES must serialize the TBI least significant bit first and the TBI most significant bit last,

as figure below illustrates.

Figure 4-20: SERDES De-Serialization Overview

de-serialization

tbi_rx_d(9:0)

1.25Gbps

Serial Stream

9

0

PHY Loopback

In PCS variations with embedded PMA targeting devices with GX transceivers, you can enable loopback on

the serial interface to test the PCS and embedded PMA functions in isolation of the PMD. To enable loopback,

set the

sd_loopback

bit in the PCS

control

register to 1.

The serial loopback option is not supported in Cyclone IV devices with GX transceiver.

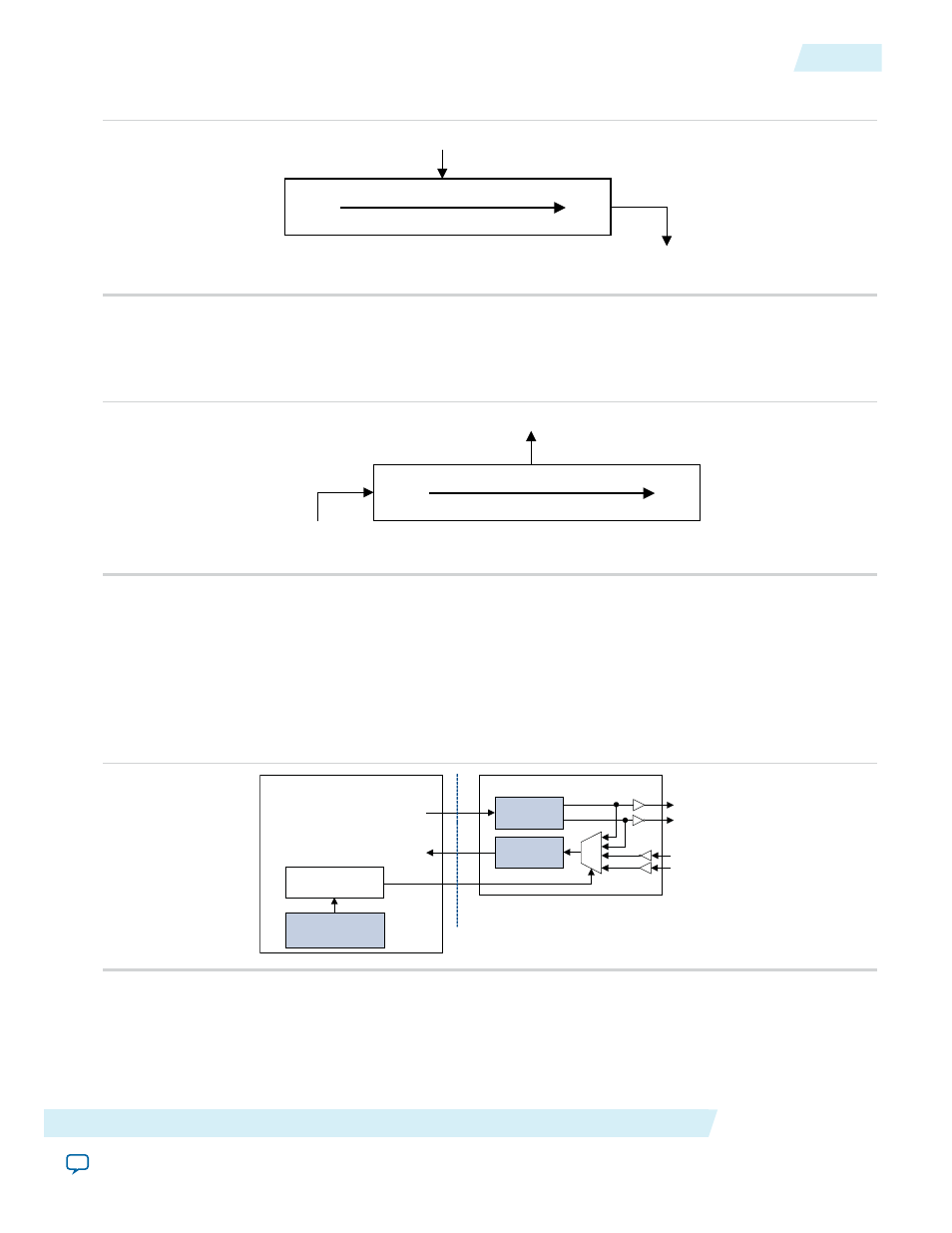

Figure 4-21: Serial Loopback

SERDES

Transmit

SERDES

Receive

SERDES

Serial Receive

Serial Transmit

PCS Transmit

PCS Receive

sd _ loopback

Control

MDIO

Slave

1000BASE-X PCS

Ten-bit

Interface

PHY Power-Down

Power-down is controlled by the

POWERDOWN

bit in the PCS

control

register. When the system management

agent enables power-down, the PCS function drives the

powerdown

signal, which can be used to control a

technology specific circuit to switch off the PCS function clocks to reduce the application activity.

Altera Corporation

Functional Description

4-33

PHY Loopback

UG-01008

2014.06.30