Altera Triple Speed Ethernet MegaCore Function User Manual

Page 82

The testbenches comprise the following modules:

• Device under test (DUT)—the design example.

• Avalon driver—uses Avalon-ST master bus functional models (BFMs) to exercise the transmit and receive

paths. The driver also uses the master Avalon-MM BFM to access the Avalon-MM interfaces of the design

example components.

• Packet monitors—monitors the transmit and receive datapaths, and displays the frames in the simulator

console.

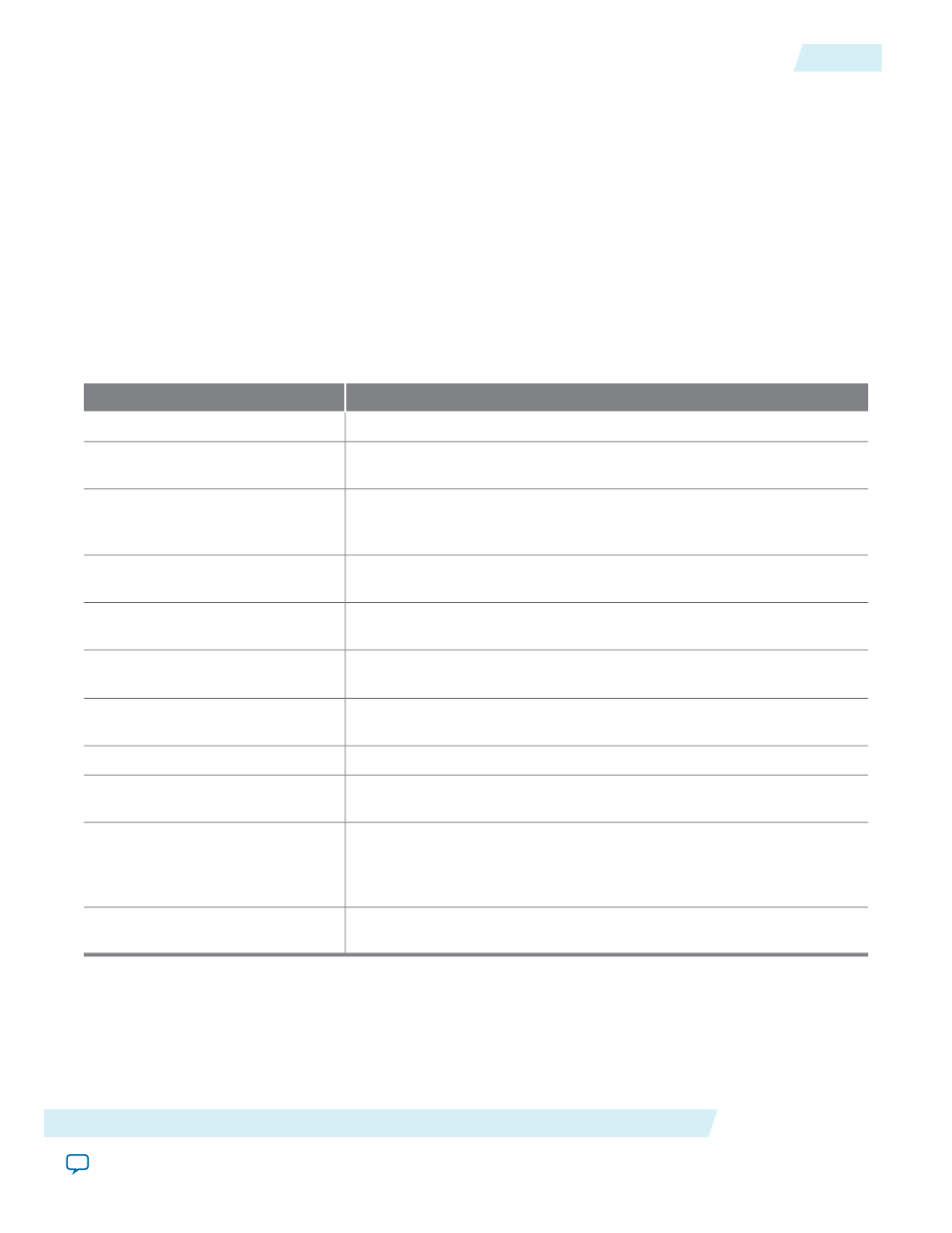

Triple-Speed Ethernet with IEEE 1588v2 Testbench Files

The <ip library>/ethernet/altera_eth_tse_design_example/tse_ieee1588/ testbench directory contains the

testbench files.

Table 5-3: Triple-Speed Ethernet with IEEE 1588v2 Testbench Files

Description

File Name

A wrapper for the Avalon BFMs that the

avalon_driver.sv

file uses.

avalon_bfm_wrapper.sv

A SystemVerilog HDL driver that utilizes the BFMs to exercise the

transmit and receive path, and access the Avalon-MM interface.

avalon_driver.sv

A SystemVerilog HDL testbench that contains parameters to configure

the BFMs. Because the configuration is specific to the DUT, you must

not change the contents of this file.

avalon_if_params_pkg.sv

A SystemVerilog HDL testbench that monitors the Avalon-ST transmit

and receive interfaces.

avalon_st_eth_packet_monitor.sv

A SystemVerilog HDL package that contains the default parameter settings

of the testbench.

default_test_params_pkg.sv

A SystemVerilog HDL class that defines the Ethernet frames. The

avalon_

driver.sv

file uses this class.

eth_mac_frame.sv

A SystemVerilog HDL package that maps addresses to the Avalon-MM

control registers.

eth_register_map_params_pkg.sv

A SystemVerilog HDL class that defines the timestamp in the testbench.

ptp_timestamp.sv

A SystemVerilog HDL testbench file that controls the flow of the

testbench.

tb_testcase.sv

The top-level testbench file. This file includes the customized Triple-

Speed Ethernet MAC, which is the device under test (DUT), a client

packet generator, and a client packet monitor along with other logic

blocks.

tb_top.sv

A signal tracing macro script for use with the ModelSim simulation

software to display testbench signals.

wave.do

Triple-Speed Ethernet with IEEE 1588v2 Testbench Simulation Flow

Upon a simulated power-on reset, each testbench performs the following operations:

1. Initializes the DUT by configuring the following options through the Avalon-MM interface:

Altera Corporation

Triple-Speed Ethernet with IEEE 1588v2 Design Example

5-5

Triple-Speed Ethernet with IEEE 1588v2 Testbench Files

UG-01008

2014.06.30