Connecting mac to external phys, Gigabit ethernet, Connecting mac to external phys -22 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 58

Description

Name

The PHY device address (PHYAD). Up to 32 devices can be addressed. For PHY device 0, the

Addr1 field is set to the value configured in the

mdio_addr0

register. For PHY device 1, the

Addr1 field is set to the value configured in the

mdio_addr1

register.

Addr1

Register Address. Each PHY can have up to 32 registers.

Addr2

Turnaround time. Two bit times are reserved for read operations to switch the data bus from

write to read for read operations. The PHY device presents its register contents in the data phase

and drives the bus from the 2

nd

bit of the turnaround phase.

TA

16-bit data written to or read from the PHY device.

Data

Between frames, the MDIO data signal is tri-stated.

Idle

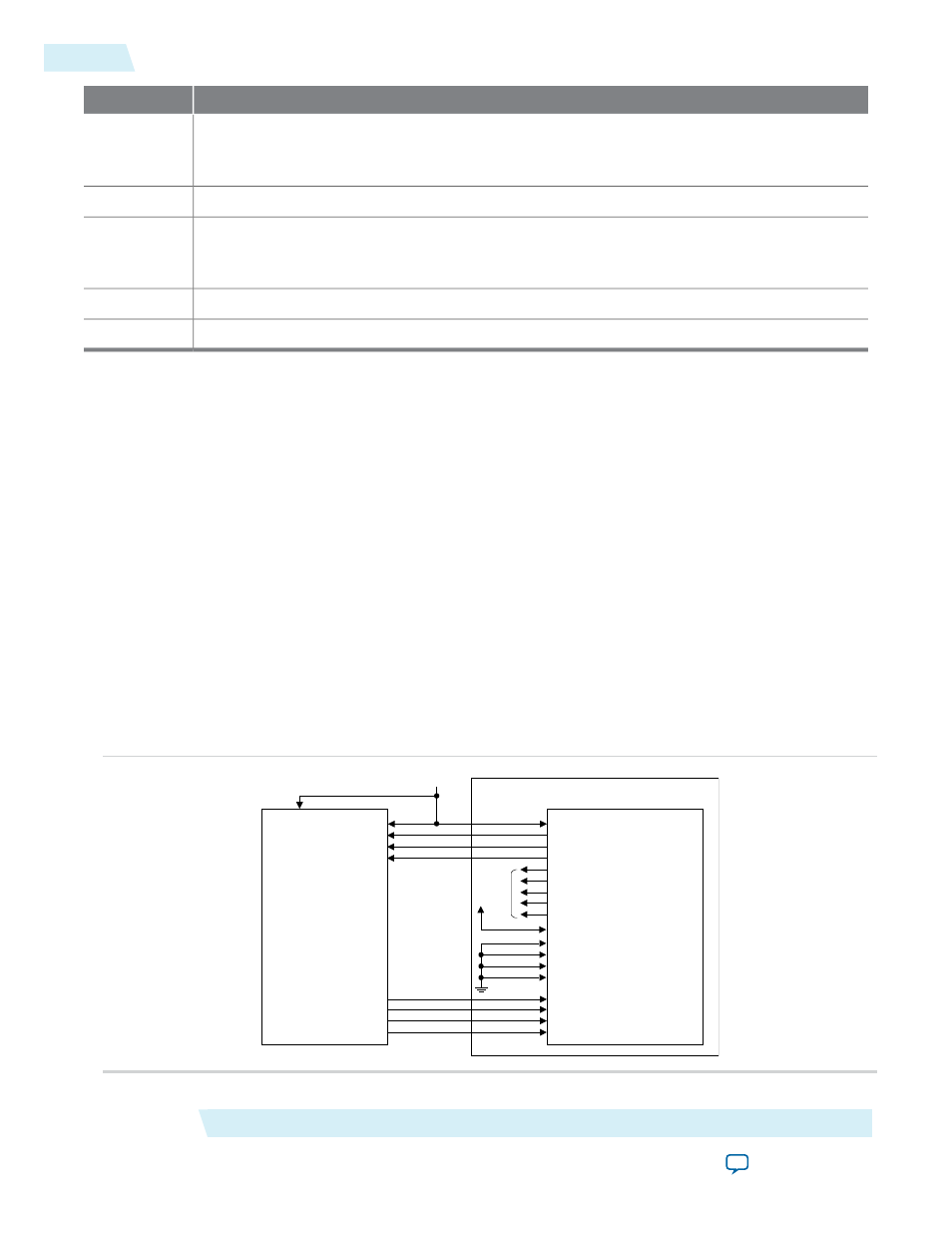

Connecting MAC to External PHYs

The MAC function implements a flexible network interface—MII for 10/100-Mbps interfaces, RGMII or

GMII for 1000-Mbps interfaces—that you can use in multiple applications. This section provides the guidelines

for implementing the following network applications:

• Gigabit Ethernet operation

• Programmable 10/100 Ethernet operation

• Programmable 10/100/1000 Ethernet operation

Gigabit Ethernet

You can connect gigabit Ethernet PHYs to the MAC function via GMII or RGMII. On the receive path,

connect the 125-MHz clock provided by the PHY device to the MAC clock,

rx_clk

. On transmit, drive a

125-MHz clock to the PHY GMII or RGMII. Connect a 125-MHz clock source to the MAC transmit clock,

tx_clk

.

A technology specific clock driver is required to generate a clock centered with the GMII or RGMII data

from the MAC. The clock driver can be a PLL, a delay line or a DDR flip-flop.

Figure 4-10: Gigabit PHY to MAC via GMII

Un

us

ed

Altera FPGA

ena_10

eth_mode

set_10

set_1000

tx_clk

m_tx_d(3:0)

m_tx_en

m_tx_err

gm_tx_d(7:0)

gm_tx_en

gm_tx_err

rx_clk

m_rx_d(3:0)

m_rx_en

gm_rx_d(7:0)

gm_rx_dv

gm_rx_err

m_rx_err

Reference Clock

125 MHz

Vcc

clk_in/xtali

gtx_clk

tx_en

tx_err

rx_clk

rx_dv

rx_err

txd(7:0)

rxd(7:0)

10/100/1000

Ethernet

MAC

Gigabit

PHY

Functional Description

Altera Corporation

UG-01008

Connecting MAC to External PHYs

4-22

2014.06.30