Transmit and receive, Command registers (dword offset 0x3a – 0x3b) – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 96

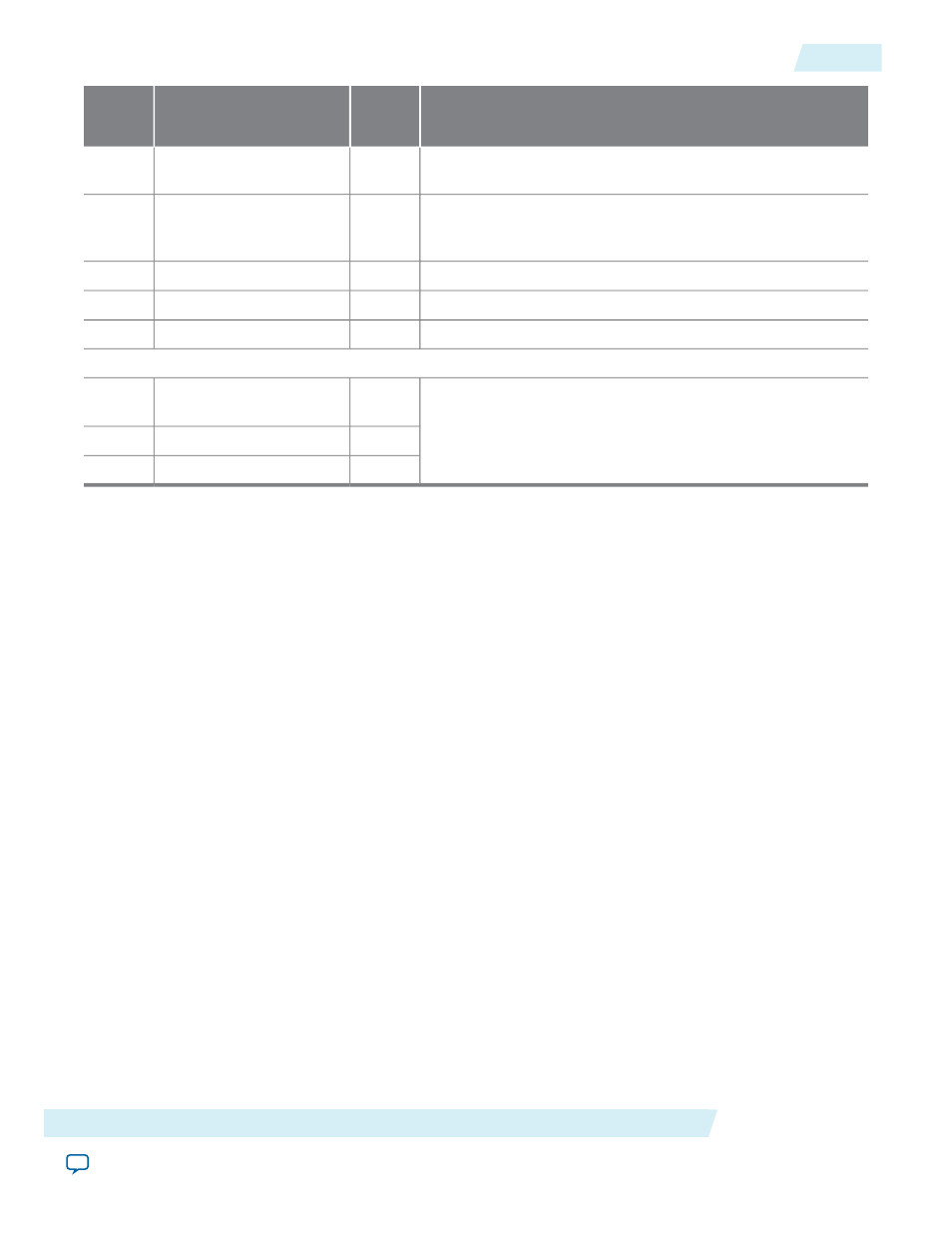

Description

R/W

Name

Dword

Offset

The number of received good and errored frames between the

length of 1024 and 1518 bytes.

RO

etherStatsPkts1024to1518Octets

0x35

The number of received good and errored frames between the

length of 1519 and the maximum frame length configured in

the

frm_length

register.

RO

etherStatsPkts1519toXOctets

0x36

Too long frames with CRC error.

RO

etherStatsJabbers

0x37

Too short frames with CRC error.

RO

etherStatsFragments

0x38

Unused

—

Reserved

0x39

Extended Statistics Counters (0x3C – 0x3E)

Upper 32 bits of the respective statistics counters. By default

all statistics counters are 32 bits wide. These statistics counters

can be extended to 64 bits by turning on the Enable 64-bit

byte counters parameter.

RO

msb_

aOctetsTransmittedOK

0x3C

RO

msb_aOctetsReceivedOK

0x3D

RO

msb_etherStatsOctets

0x3E

Transmit and Receive Command Registers (Dword Offset 0x3A – 0x3B)

describes the registers that determine how the MAC function processes transmit and receive

frames. A software reset does not change the values in these registers.

Altera Corporation

Configuration Register Space

6-13

Transmit and Receive Command Registers (Dword Offset 0x3A – 0x3B)

UG-01008

2014.06.30