Recommended clock frequency, Recommended clock frequency -3 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 173

Recommended Clock Frequency

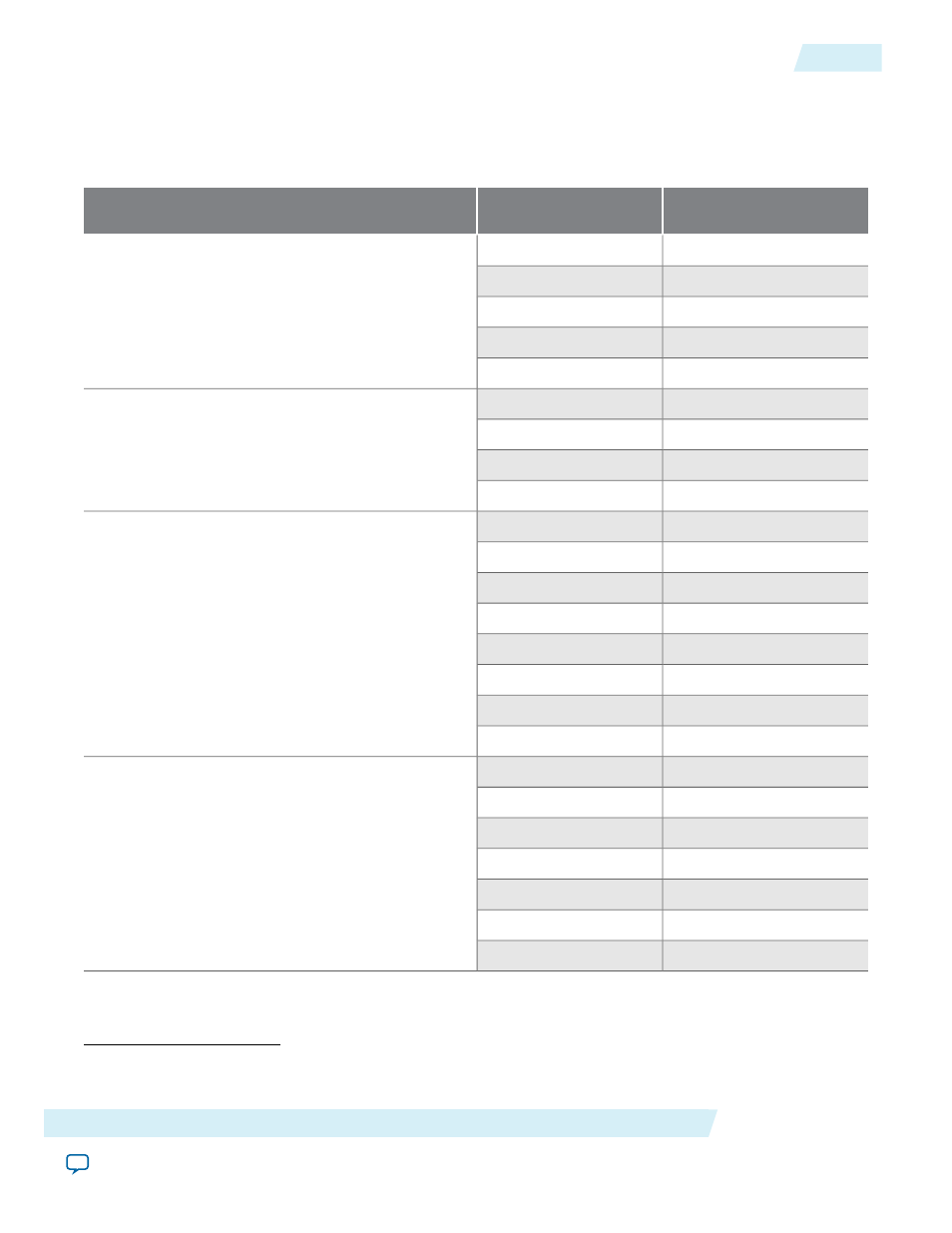

Table 9-1: Recommended Clock Input Frequency For Each MegaCore Function Variant

Recommended Frequency

(MHz)

Clock

MegaCore Function Variant

50–100

CLK

10/100/1000-Mbps Ethernet MAC (with Internal FIFO

buffers)

125

TX_CLK

125

RX_CLK

100

FF_TX_CLK

100

FF_RX_CLK

50–100

CLK

10/100/1000-Mbps Ethernet MAC (without Internal

FIFO buffers)

125

TX_CLK <N>

125

RX_CLK <N>

100

RX_AFULL_CLK

50–100

CLK

10/100/1000-Mbps Ethernet MAC with 1000BASE-

X/SGMII PCS (with Internal FIFO buffers)

100

FF_TX_CLK

100

FF_RX_CLK

125

TBI_TX_CLK

125

TBI_RX_CLK

125

REF_CLK

37.5–50

RECONFIG_CLK

(2)

125

GXB_CAL_BLK_CLK

50–100

CLK

10/100/1000-Mbps Ethernet MAC with 1000BASE-

X/SGMII PCS (without Internal FIFO buffers)

100

RX_AFULL_CLK

125

TBI_TX_CLK <N>

125

TBI_RX_CLK <N>

125

REF_CLK

37.5–50

RECONFIG_CLK <N>

(2)

125

GXB_CAL_BLK_CLK

(2)

This signal is only applicable to all device family prior to the 28-nm devices, which consists of the Stratix V,

Arria V, Arria V GZ, and Cyclone V devices.

Altera Corporation

Timing Constraints

9-3

Recommended Clock Frequency

UG-01008

2014.06.30