Tbi interface signals, Description i/o name – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 131

Section

Interface Signal

Pause and Magic Packet Signals

on page 7-8

Pause and magic packet signals

on page 7-9

MII/GMII/RGMII interface

on page 7-10

PHY management signals

on page 7-11

ECC status signals

10/100/1000 Ethernet MAC with 1000BASE-X/SGMII PCS Signals

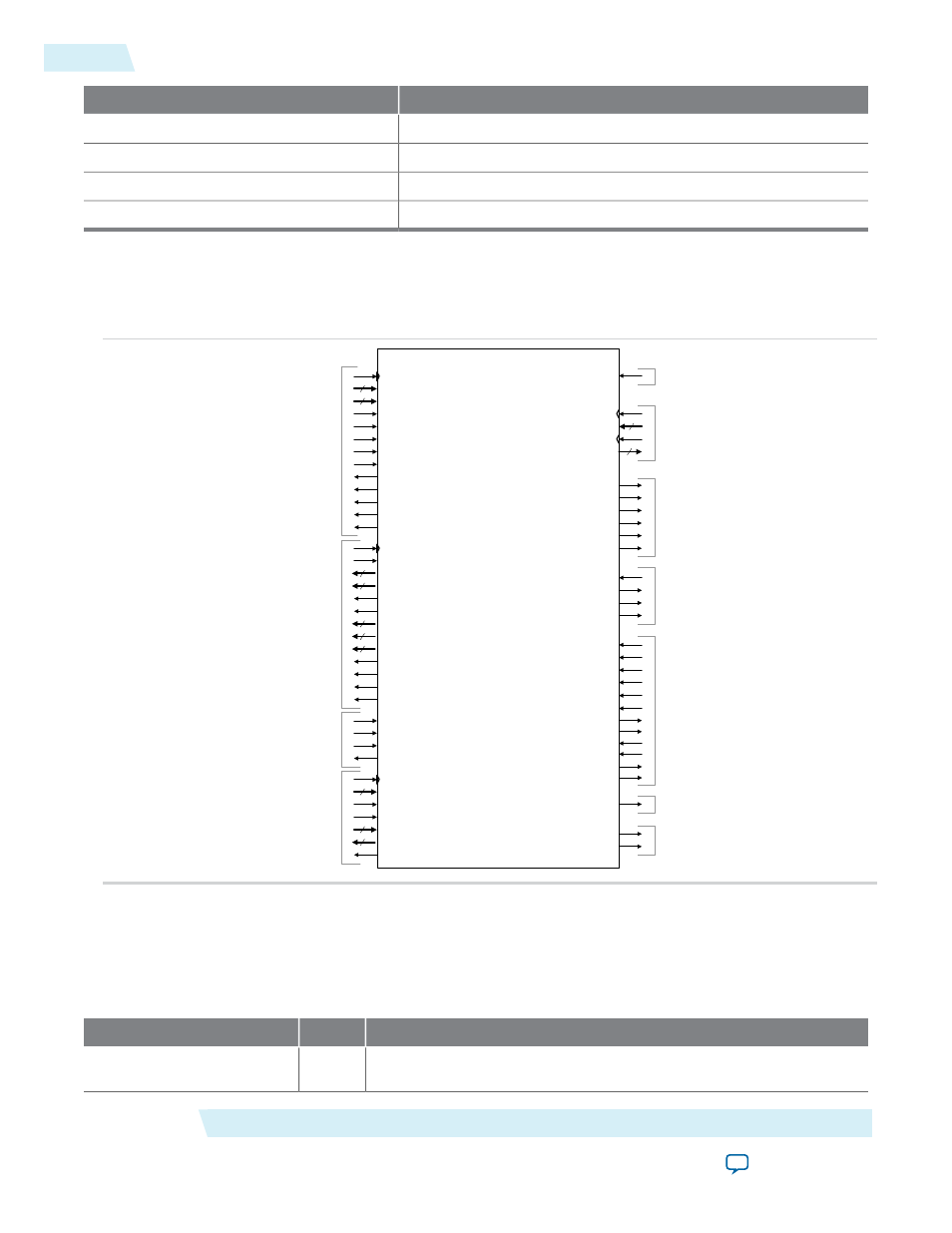

Figure 7-3: 10/100/1000 Ethernet MAC Function with Internal FIFO Buffers, with 1000BASE-X/SGMII PCS

Signals

10/100/1000 Ethernet MAC with 1000Base -X PCS /SGMII

Reset

Signal

reset

Status

LED

Signals

led_an

led_crs

led_col

led_char _err

led_link

led_disp _err

PHY

Management

Signals

mdio_in

mdc

mdio_oen

mdio_out

SERDES

Control

Signals

sd _loopback

powerdown

Pause and Magic

Packet Signals

xon _gen

xoff_gen

magic _wakeup

magic _sleep _n

n

2

MAC Transmit

Interface Signals

ff_tx_crc _fwd

ff_tx_eop

ff_tx_err

ff_tx_sop

ff_tx_wren

tx_ff_uflow

ff_tx_clk

ff_tx_rdy

ff_tx_septy

ff_tx_mod[1:0]

ff_tx_a_full

ff_tx_a_empty

n

2

6

18

4

MAC Receive

Interface Signals

ff_rx_mod[1:0]

ff_rx_eop

ff_rx_sop

rx_err[5:0]

rx_err_stat[17:0]

rx_frm_type[3:0]

ff_rx_dsav

ff_rx_rdy

ff_rx_clk

ff_rx_dval

ff_rx_a_full

ff_rx_a_empty

8

32

32

MAC Control

Interface

Signals

clk

address [7:0]

read

write

readdata [31:0]

writedata [31:0]

waitrequest

Ten Bit

Interface

Signals

tbi_rx_clk

tbi_rx_d[9:0]

tbi_tx_clk

tbi_tx_d[9:0]

10

10

ECC

Status

Signal

pcs _eccstatus [1:0]

Arria 10

Transceiver

Native PHY

Signals

tx_serial _clk

rx_cdr _refclk

tx_analogreset

tx_digitalreset

rx_analogreset

rx_digitalreset

tx_cal _busy

rx_cal _busy

rx_set _locktodata

rx_set _locktoref

rx_is_locktodata

rx_is_locktoref

ff_rx_data[DATAWIDTH-1:0]

ff_tx_data[DATAWIDTH-1:0]

TBI Interface Signals

If the core variation does not include an embedded PMA, the PCS block provides a 125-MHz ten-bit interface

(TBI) to an external SERDES chip.

Table 7-19: TBI Interface Signals for External SERDES Chip

Description

I/O

Name

TBI transmit data. The PCS function transmits data on this bus

synchronous to

tbi_tx_clk

.

O

tbi_tx_d(9:0)

Interface Signals

Altera Corporation

UG-01008

10/100/1000 Ethernet MAC with 1000BASE-X/SGMII PCS Signals

7-16

2014.06.30