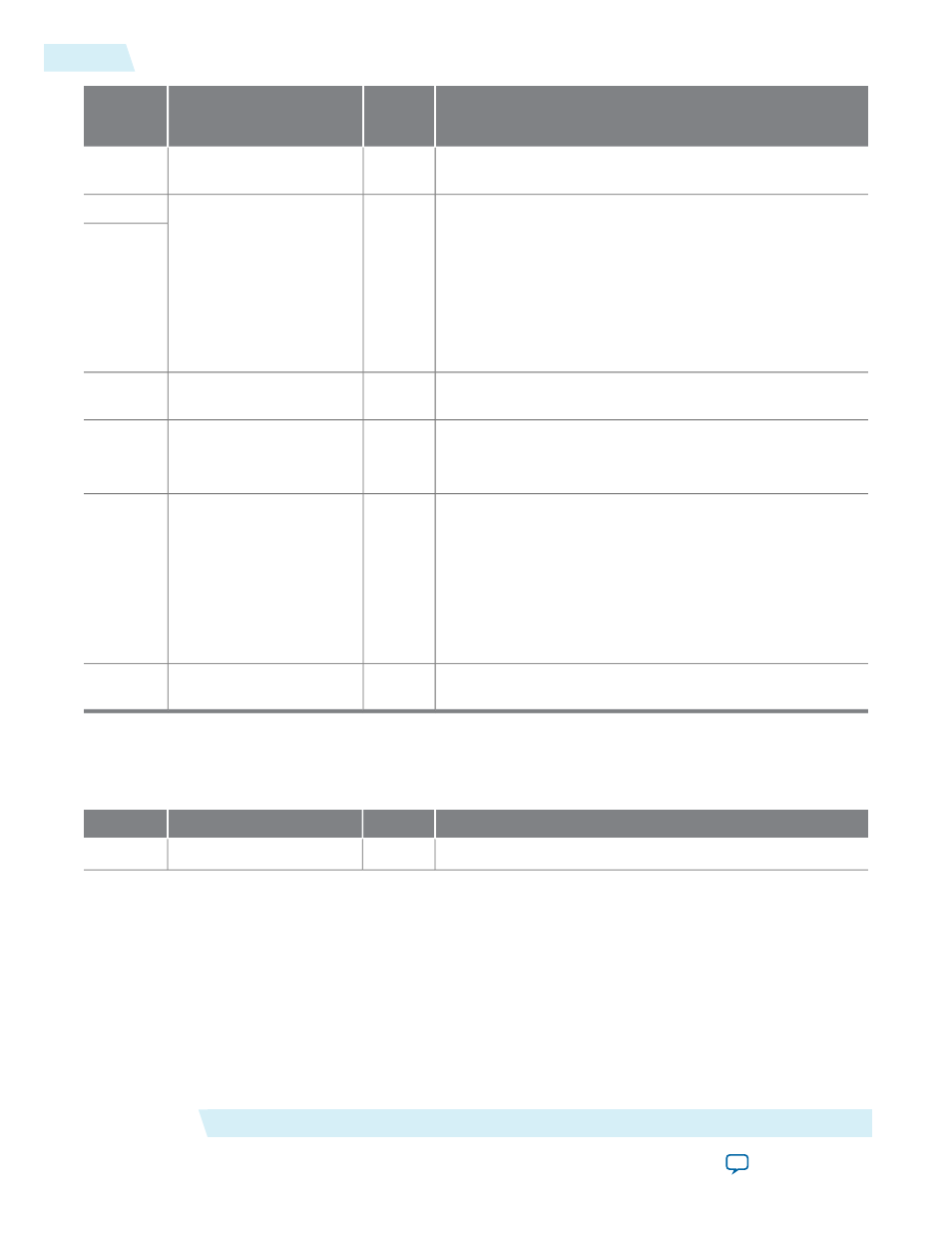

Control register (word offset 0x00), Control register (word offset 0x00) -20 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 103

Description

R/W

Register Name

Word

Offset

The PCS function revision. Always set to the current version

of the MegaCore function.

RO

rev

0x11

21-bit auto-negotiation link timer. Set the link timer value

from 0 to 16 ms in 8 ns steps (125 MHz clock periods). The

reset value sets the link timer to 10 ms.

• Bits 15:0 are written to word offset 0x12. Bit 0 of word

offset 0x12 is always set to 0, thus any value written to it

is ignored.

• Bits 20:16 are written to word offset 0x13. The remaining

bits are reserved and always set to 0.

RW

link_timer

0x12

0x13

Interface mode. Use this register to specify the operating

mode of the PCS function; 1000BASE-X or SGMII.

RW

if_mode

0x14

• Bit[0]—Set this bit to 1 to disable PCS register read

timeout.

• Bits[31:1]—unused. Set to read-only value 0.

RW

disable_read_timeout

0x15

• Bit[0]—PCS register read timeout indication. Valid only

when

disable_read_timeout

is set to 0. This bit is

cleared after it is read.

The PCS function sets this bit to 0 when the register read

ends normally; and sets this bit to 1 when the register

read ends with a timeout.

• Bits[31:1]—unused.

RO

read_timeout

0x16

—

—

Reserved

0x17 –

0x1F

Control Register (Word Offset 0x00)

Table 6-13: PCS Control Register Bit Descriptions

Description

R/W

Name

Bit(s)

—

—

Reserved

0:4

Configuration Register Space

Altera Corporation

UG-01008

Control Register (Word Offset 0x00)

6-20

2014.06.30