Altera Triple Speed Ethernet MegaCore Function User Manual

Page 172

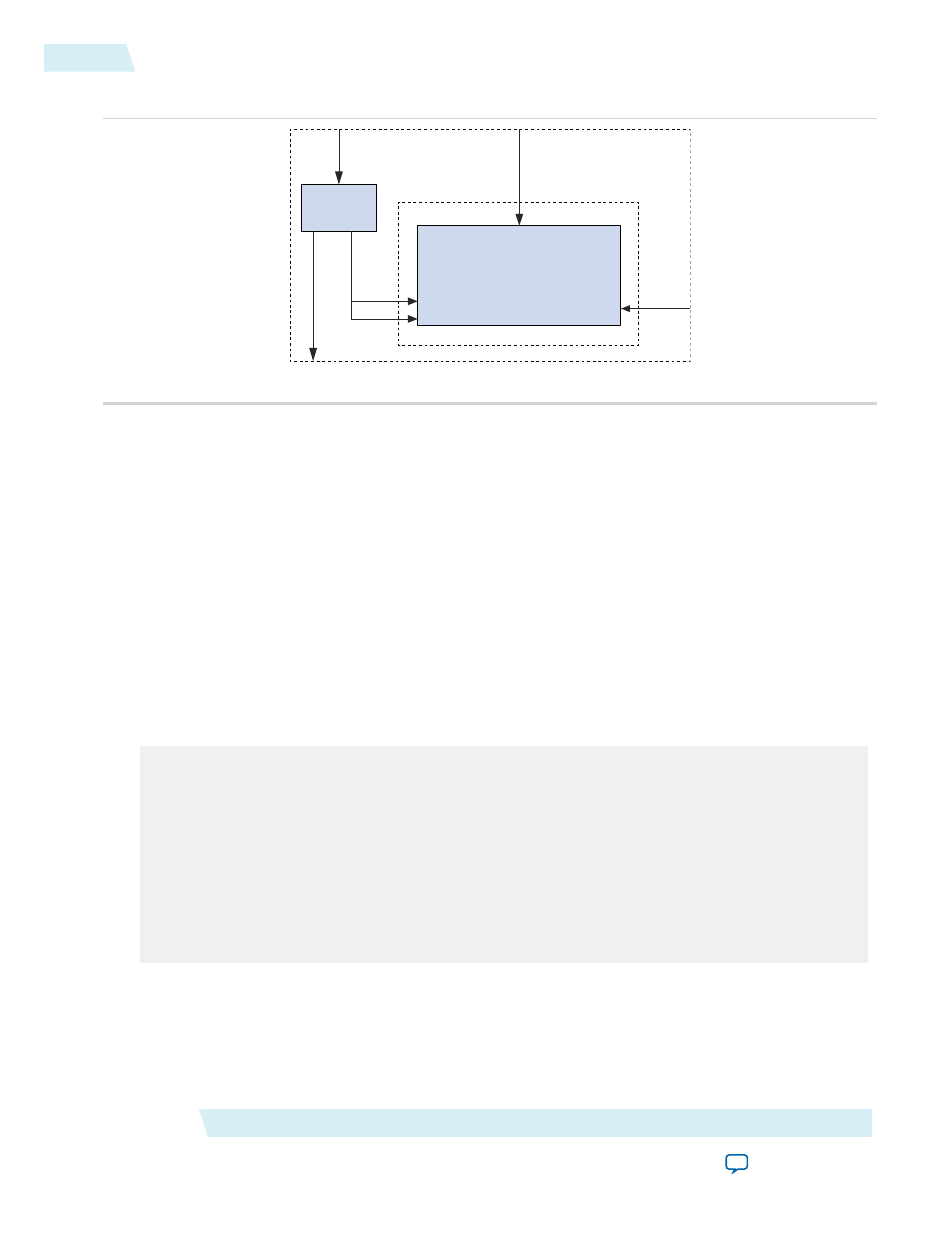

Figure 9-1: Triple-Speed Ethernet Timing Constraint Example

user_instance.v

TOP.v

Altera PLL

10/100/1000-Mbps Ethernet MAC

with 1000BASE-X/SGMII

PCS and PMA

(with internal FIFO)

ff_tx_clk

ff_rx_clk

tse_variation.v

ref_clk

clk

ext_clk

pll_inclk

100-Mhz

50-Mhz

110-Mhz

inclk0

c1

c0

xcvr_ref_clk

125-Mhz

Note to

1.

reconfig_clk

is not shown in this example. Constrain

reconfig_clk

based on your design implemen-

tation.

The example in above consists of the following Verilog modules:

•

TOP.v

—The top level design module which contains an Altera PLL and a user-defined instance. The top

level input clocks consist of

pll_inclk

,

ext_clk

, and

xcvr_ref_clk

.

•

user_instance.v

—The user-defined instance that instantiates the Triple-Speed Ethernet MegaCore function.

•

tse_variation.v

—A Triple-Speed Ethernet MegaCore function variation. This example uses a 10/100/1000-

Mbps Ethernet MAC with an internal FIFO buffer, a 1000BASE-X/SGMII PCS, and an embedded PMA.

The frequency for the PLL clock input,

inclk0

, is 100 MHz, and the frequency for the PLL clock output,

c0

,

is 110 MHz. The Triple-Speed Ethernet MAC Avalon-ST clocks,

ff_tx_clk

and

ff_rx_clk

, use

c0

as the

clock source. The input clock frequency for the transceiver reference clock,

xcvr_ref_clk

, is 125 MHz.

Example of the Triple-Speed Ethernet MegaCore function timing constraint file:

# PLL clock input, 100 MHz

create_clock -name pll_inclk -period 10.000 [get_ports {pll_inclk}]

# ext_clk, 50 MHz

create_clock -name ext_clk -period 20.000 [get_ports {pll_ext_clk}]

# xcvr_ref_clk, 125 MHz

create_clock -name xcvr_ref_clk -period 8.000 [get_ports {xcvr_ref_clk}]

# Derive PLL generated output clocks.

derive_pll_clocks

Timing Constraints

Altera Corporation

UG-01008

Creating Clock Constraints

9-2

2014.06.30