Altera Triple Speed Ethernet MegaCore Function User Manual

Page 120

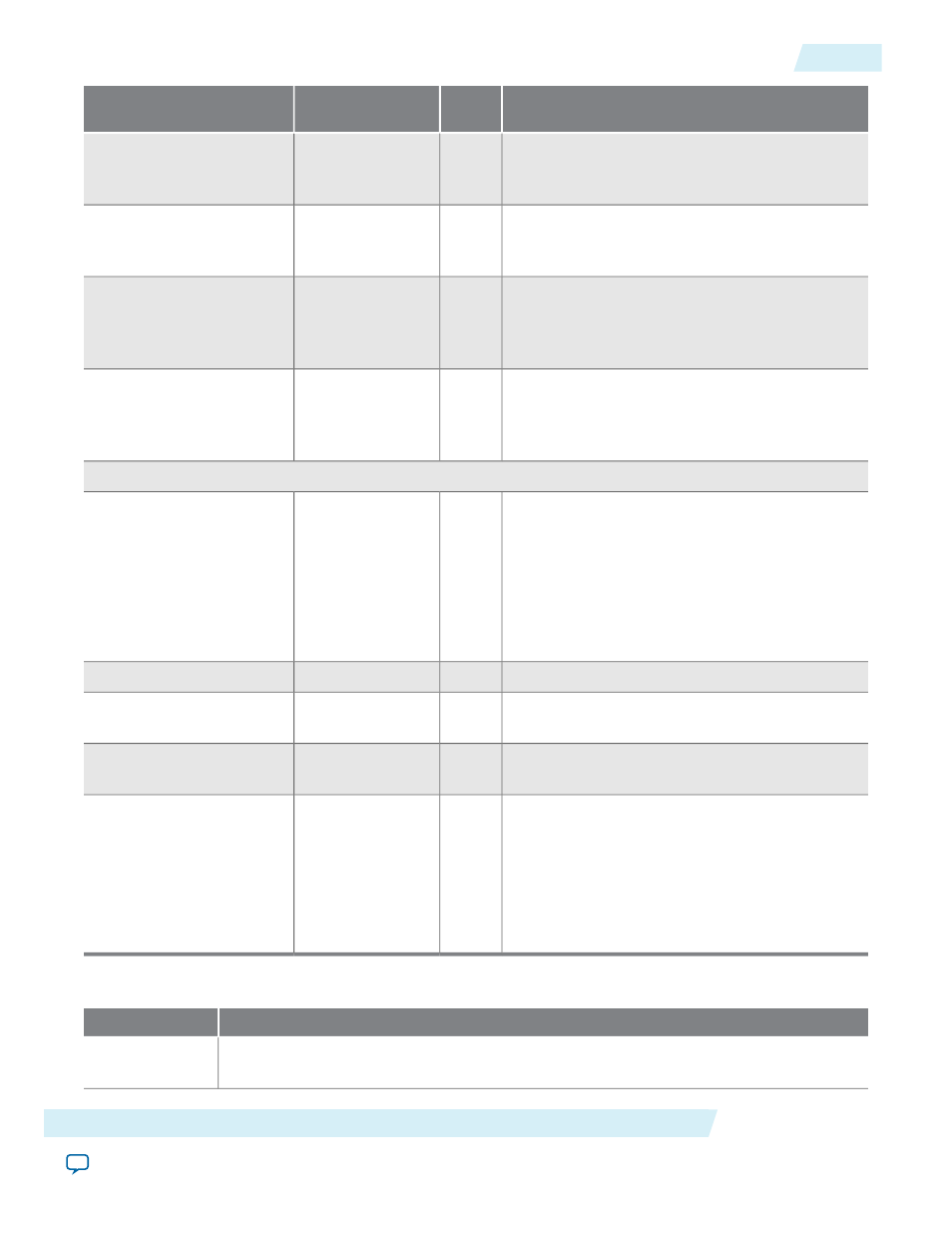

Description

I/O

Avalon-ST Signal

Type

Name

Receive start of packet. Asserted when the first

byte or word of a frame is driven on

ff_rx_

data[(DATAWIDTH-1):0]

.

O

startofpacket

ff_rx_sop

Receive end of packet. Asserted when the last byte

or word of frame data is driven on

ff_rx_

data[(DATAWIDTH-1):0]

.

O

endofpacket

ff_rx_eop

Receive application ready. Assert this signal on

the rising edge of

ff_rx_clk

when the user

application is ready to receive data from the MAC

function.

I

ready

ff_rx_rdy

Receive error. Asserted with the final byte in the

frame to indicate that an error was detected when

receiving the frame. See

for the bit

description.

O

error

rx_err[5:0]

Component-Specific Signals

Receive frame available. When asserted, this signal

indicates that the internal receive FIFO buffer

contains some data to be read but not necessarily

a complete frame. The user application may want

to start reading from the FIFO buffer.

This signal remains deasserted in the store and

forward mode.

O

—

ff_rx_dsav

Frame type. See

for the bit description.

O

—

rx_frm_type[3:0]

Asserted when the FIFO buffer reaches the almost-

full threshold.

O

—

ff_rx_a_full

Asserted when the FIFO buffer goes below the

almost-empty threshold.

O

—

ff_rx_a_empty

rx_err_stat[17]

: One indicates that the receive

frame is a stacked VLAN frame.

rx_err_stat[16]

: One indicates that the receive

frame is either a VLAN or stacked VLAN frame.

rx_err_stat[15:0]

: The value of the length/type

field of the receive frame.

O

—

rx_err_stat[17:0]

Table 7-6: rx_frm_type Bit Description

Description

Bit

Indicates VLAN frames. Asserted with

ff_rx_sop

and remains asserted until the end of the

frame.

3

Altera Corporation

Interface Signals

7-5

MAC Receive Interface Signals

UG-01008

2014.06.30