1000base-x – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 106

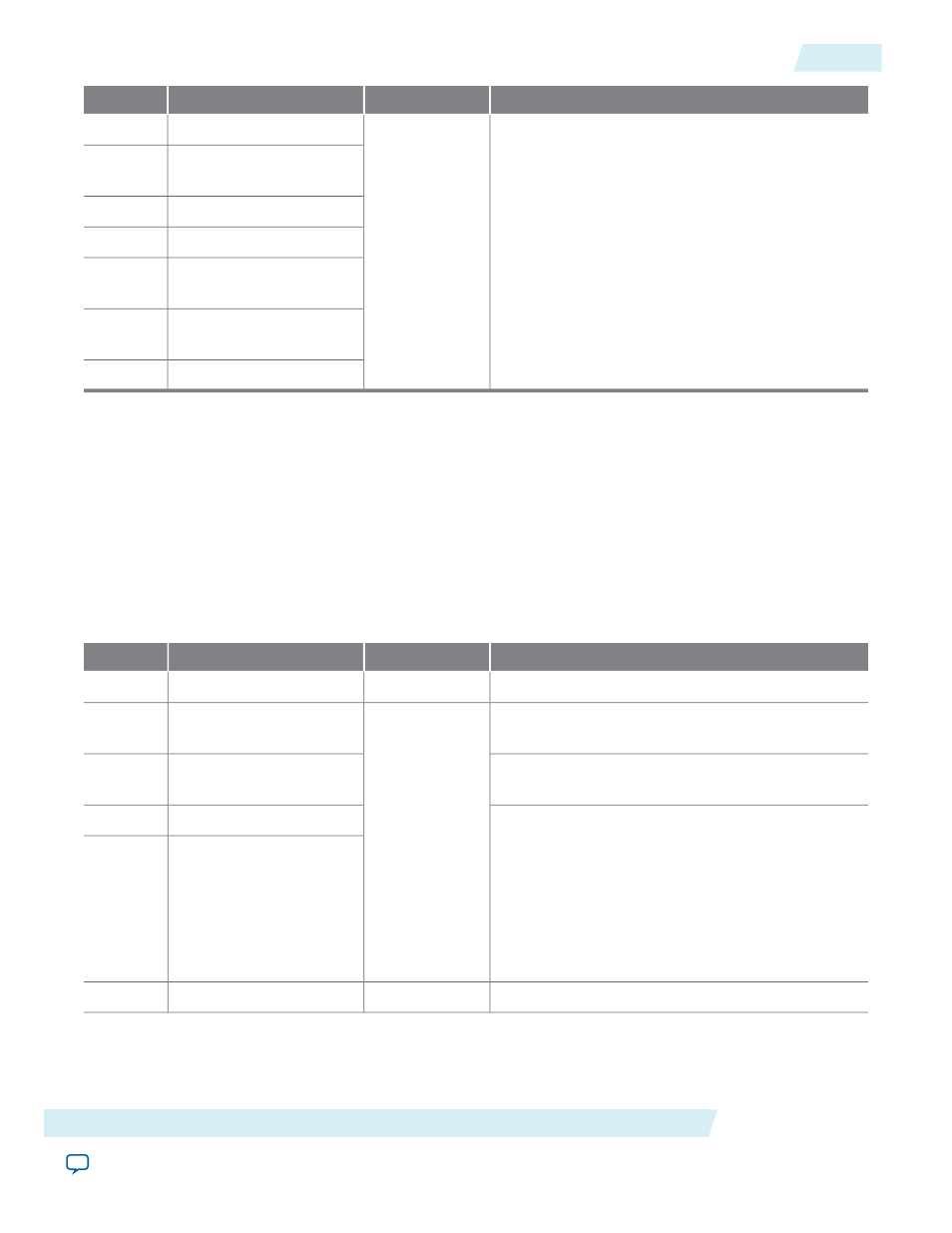

Description

R/W

Name

Bit

The PCS function does not support 100Base-T2,

10-Mbps, 100BASE-X, and 100Base-T4 operation.

Always set to 0.

RO

100BASET2_HALF_DUPLEX

9

100BASET2_FULL_

DUPLEX

10

10MBPS_HALF_DUPLEX

11

10MBPS_FULL_DUPLEX

12

100BASE-X_HALF_

DUPLEX

13

100BASE-X_FULL_

DUPLEX

14

100BASE-T4

15

Dev_Ability and Partner_Ability Registers (Word Offset 0x04 – 0x05)

The definition of each field in the

partner_ability

registers depends on the mode in which the PCS function

operates.

In this mode, the definition of the fields in the

dev_ability

register are the same as the fields in the

partner_ability

register. The contents of these registers are valid only when the auto-negotiation completes

(

AUTO_NEGOTIATION_COMPLETE

bit in the

status

register = 1).

1000BASE-X

Table 6-15: Dev_Ability and Partner_Ability Registers Bits Description in 1000BASE-X

Description

R/W

Name

Bit(s)

Always set these bits to 0.

—

Reserved

0:4

Full-duplex mode enable. A value of 1 indicates

support for full duplex.

FD

5

Half-duplex mode enable. A value of 1 indicates

support for half duplex.

HD

6

Pause support.

•

PS1

=0 /

PS2

=0: Pause is not supported.

•

PS1

=0 /

PS2

=1: Asymmetric pause toward link

partner.

•

PS1

=1 /

PS2

=0: Symmetric pause.

•

PS1

=1/

PS2

=1: Pause is supported on transmit

and receive.

PS1

7

PS2

8

Always set these bits to 0.

—

Reserved

9:11

Altera Corporation

Configuration Register Space

6-23

Dev_Ability and Partner_Ability Registers (Word Offset 0x04 – 0x05)

UG-01008

2014.06.30