Tod clock avalon-st transmit interface signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 204

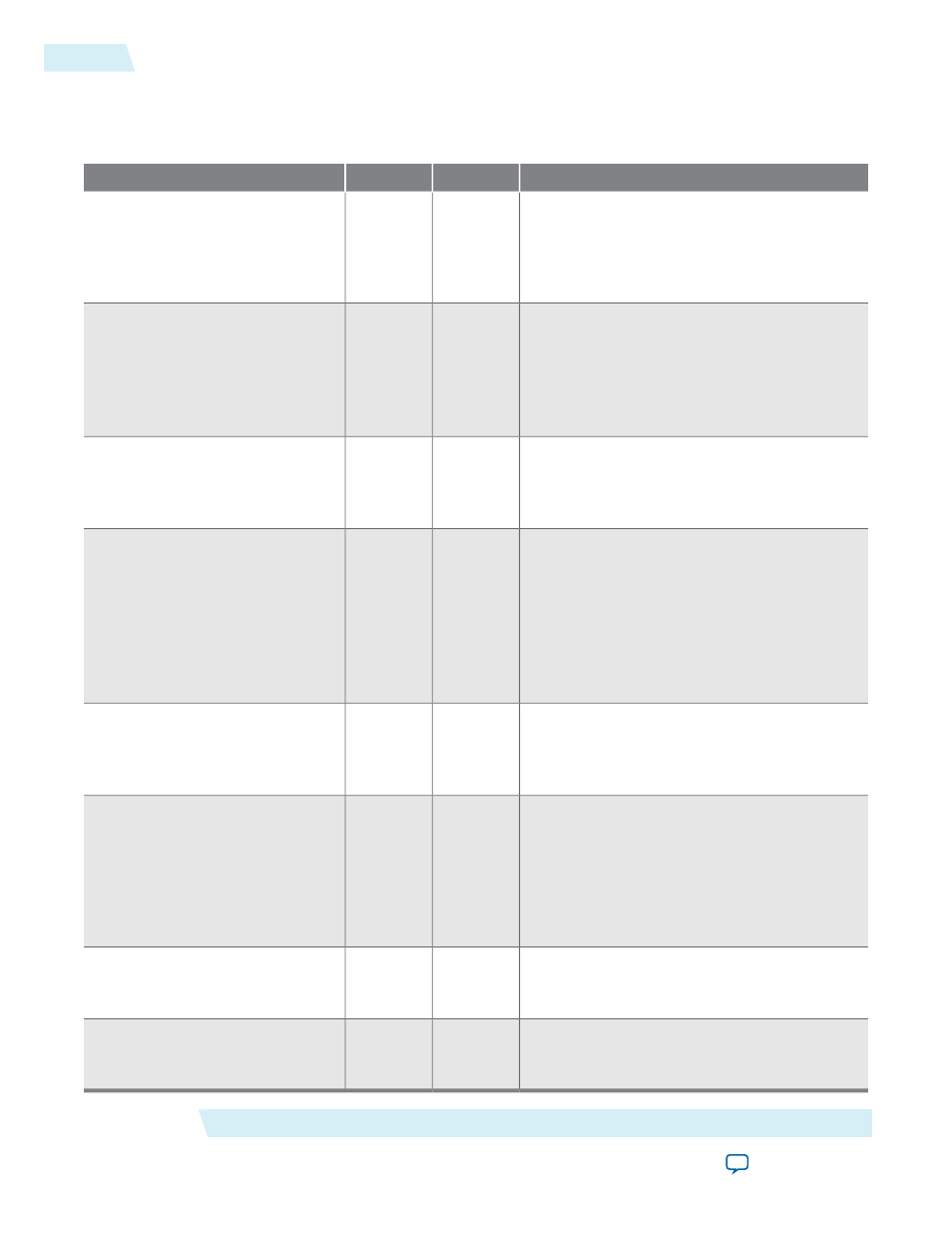

ToD Clock Avalon-ST Transmit Interface Signals

Table C-5: Avalon-ST Transmit Interface Signals for ToD Clock

Description

Width

Direction

Signal

Timestamp from the ToD clock

• Bits 0 to 15: 16-bit fractional nanosecond

field

• Bits 16 to 63: 48-bit nanosecond field

64

Output

time_of_day_64b[]

Timestamp from the ToD clock

• Bits 0 to 15: 16-bit fractional nanosecond

field

• Bits 16 to 47: 32-bit nanosecond field

• Bits 48 to 95: 48-bit second field

96

Output

time_of_day_96b[]

Indicates that the synchronized ToD is valid.

Every time you assert this signal, the synchro-

nized ToD is loaded into the ToD clock. Assert

this signal for only one clock cycle.

1

Input

time_of_day_96b_load_valid

Loads 96-bit synchronized ToD from master

ToD clock to slave ToD clock within 1 clock

cycle.

• Bits 0 to 15: 16-bit fractional nanosecond

field

• Bits 16 to 63: 32-bit nanosecond field

• Bits 64 to 95: 48-bit second field

96

Input

time_of_day_96b_load_data[]

Indicates that the synchronized ToD is valid.

Every time you assert this signal, the synchro-

nized ToD is loaded into the ToD clock. Assert

this signal for only one clock cycle.

1

Input

time_of_day_64b_load_valid

Loads 64-bit synchronized ToD from master

ToD clock to slave ToD clock within 1 clock

cycle.

• Bits 0 to 15: 16-bit fractional nanosecond

field

• Bits 16 to 63: 48-bit nanosecond field

64

Input

time_of_day_64b_load_data[]

Clock for the ToD clock. The clock must be in

the same clock domain as

tx_time_of_day

and

rx_time_of_day

in the MAC function.

1

Input

period_clk

Assert this signal to reset

period_clk

to the

same clock domain as

tx_time_of_day

and

rx_time_of_day

in the MAC function.

1

Input

period_rst_n

Time-of-Day (ToD) Clock

Altera Corporation

UG-01008

ToD Clock Avalon-ST Transmit Interface Signals

C-4

2014.06.30