Altera Triple Speed Ethernet MegaCore Function User Manual

Page 85

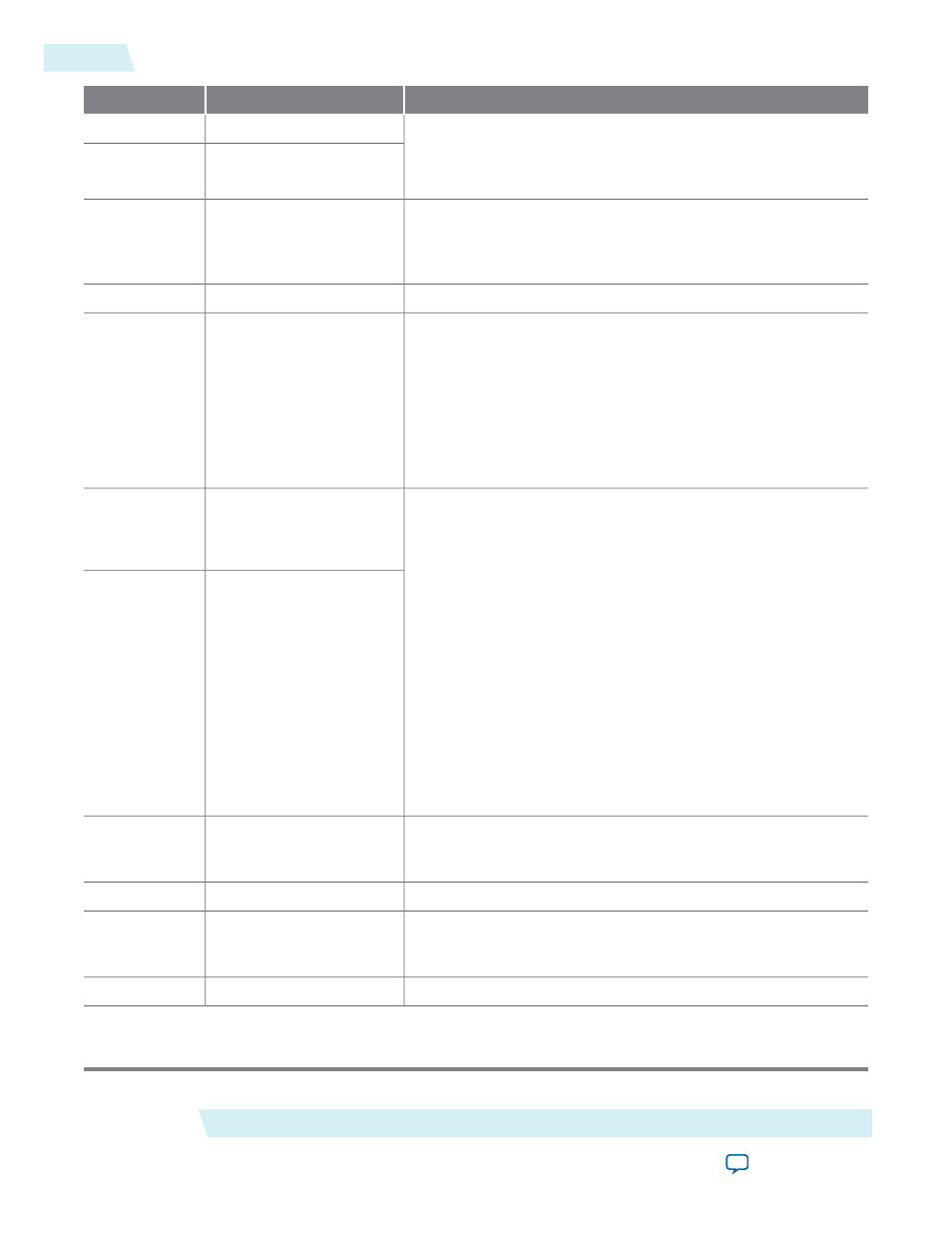

Description

Section

Dword Offset

Transmit and receive datapaths control register. For more

information about these registers, see

Command Registers (Dword Offset 0x3A – 0x3B)

on page

6-13.

Transmit Command

0x3A

Receive Command

0x3B

Upper 32 bits of selected statistics counters. These registers are

used if you turn on the option to use extended statistics counters.

For more information about these counters, refer to

Counters (Dword Offset 0x18 – 0x38)

on page 6-11 .

Extended Statistics Counters

0x3C – 0x3E

Unused.

Reserved

0x3F

64-entry write-only hash table to resolve multicast addresses.

Only bit 0 in each entry is significant. When you write a 1 to a

dword offset in the hash table, the MAC accepts all multicast

MAC addresses that hash to the value of the address (bits 5:0).

Otherwise, the MAC rejects the multicast address. This table is

cleared during reset.

Hashing is not supported in 10/100 and 1000 Mbps Small MAC

core variations.

Multicast Hash Table

0x40 – 0x7F

MDIO Space 0 and MDIO Space 1 map to registers 0 to 31 of

the PHY devices whose addresses are configured in the

mdio_

addr0

and

mdio_addr1

registers respectively. For example,

register 0 of PHY device 0 maps to dword offset 0x80, register 1

maps to dword offset 0x81 and so forth.

Reading or writing to MDIO Space 0 or MDIO Space 1

immediately triggers a corresponding MDIO transaction to read

or write the PHY register. Only bits [15:0] of each register are

significant. Write 0 to bits [31:16] and ignore them on reads.

If your variation does not include the PCS function, you can use

MDIO Space 0 and MDIO Space 1 to map to two PHY devices.

If your MAC variation includes the PCS function, the PCS

function is always device 0 and its configuration registers (

on page 6-18) occupy MDIO

Space 0. You can use MDIO Space 1 to map to a PHY device.

MDIO Space 0

or PCS Function Configura-

tion

0x80 – 0x9F

MDIO Space 1

0xA0 – 0xBF

Supplementary unicast addresses. For more information about

these addresses, refer to

Supplementary Address (Dword Offset

on page 6-15.

Supplementary Address

0xC0 – 0xC7

Unused.

Reserved

0xC8 – 0xCF

Registers to configure the IEEE 1588v2 feature. For more

information about these registers, refer to

on page 6-16.

IEEE 1588v2 Feature

0xD0 – 0xD6

Unused.

Reserved

0xD7 – 0xFF

Note to

:

1. Altera recommends that you set all bits in the reserved registers to 0 and ignore them on reads.

Configuration Register Space

Altera Corporation

UG-01008

MAC Configuration Register Space

6-2

2014.06.30