Pma -25 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 140

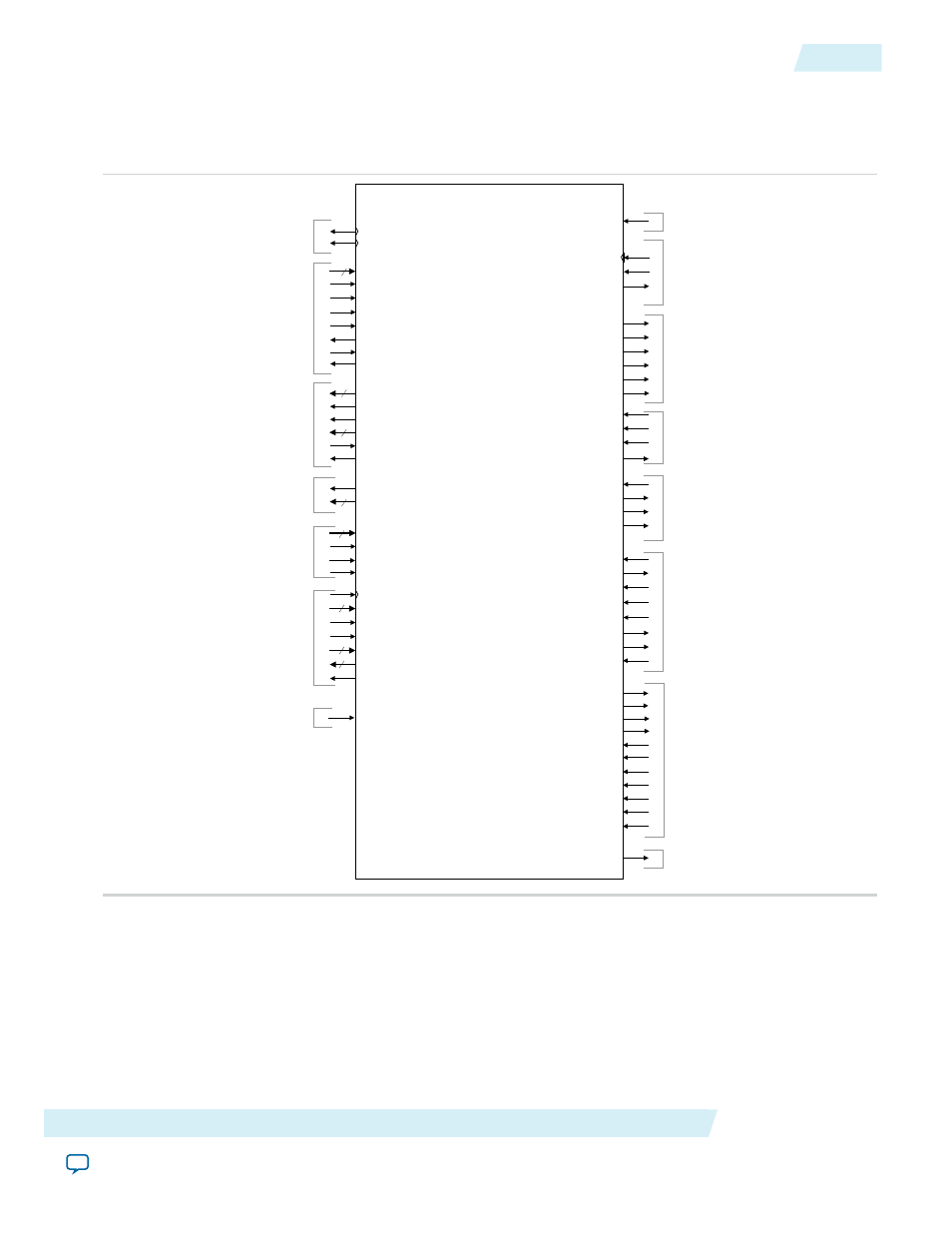

10/100/1000 Multiport Ethernet MAC with 1000BASE-X/SGMII PCS and Embedded PMA

Figure 7-6: 10/100/1000 Multiport Ethernet MAC Function without Internal FIFO Buffers, with IEEE 1588v2,

1000BASE-X/SGMII PCS and Embedded PMA Signals

PHY

Management

Signals

mdio_in

mdc

mdio_oen

mdio_out

Reset

Signal

reset

Transceiver

Native PHY

Signal

cdr_ref_clk_n

ECC Status

Signal

pcs_eccstatus[1:0]

1.25 Gbps

Serial Signals

ref_clk_n

rx_p_n

tx_p_n

Status

LED

Signals

led_an_n

led_crs_n

led_col_n

led_char_err_n

led_link_n

led_disp_err_n

mac_tx_clk_n

mac_rx_clk_n

Clock

Signals

xon_gen_n

xoff_gen_n

magic_wakeup_n

magic_sleep_n_n

Pause and Magic

Packet Signals

SERDES

Control

Signals

IEEE 1588v2

Signals

pcs_pwrdn_out

gxb_pwrdn_in_n

gxb_cal_blk_clk

reconfig_clk_n

reconfig_togxb_n

8

data_tx_data_n[7:0]

data_tx_eop_n

data_tx_error_n

data_tx_sop_n

data_tx_valid_n

data_tx_ready_n

MAC Transmit

Interface

Signals

tx_crc_fwd_n

tx_ff_uflow_n

8

5

data_rx_data_n[7:0]

data_rx_eop_n

data_rx_sop_n

data_rx_error_n[4:0]

data_rx_ready_n

data_rx_valid_n

MAC Receive

Interface

Signals

MAC Packet

Classification

Signals

pkt_class _valid_n

5

n

rx_afull_data[1:0]

rx_afull_valid

MAC FIFO

Status Signals

rx_afull_clk

32

n

clk

reg_rd

reg_wr

reg_data_in[31:0]

reg_busy

reg_data_out[31:0]

reg_addr[(log2 MAX_CHANNELS+7):0]

32

MAC Control

Interface Signals

rx_recovclkout

reconfig_busy

reconfig_fromgxb_n

tx_egress_timestamp_96b_n

tx_time_of_day_96b_n

tx_time_of_day_64b_n

rx_time_of_day_96b_n

rx_time_of_day_64b_n

pcs_phase_measure_clk

tx_egress_timestamp_request_n

tx_etstamp_ins_ctrl_n

tx_egress_timestamp_64b_n

rx_ingress_timestamp_96b_n

rx_ingress_timestamp_64b_n

Multi-Port MAC and 1000BASE-X/SGMII PCS

with Embedded PMA

pkt_class_data_n[4:0]

rx_afull_channel(CHANNEL_WIDTH-1:0)

Note to

:

1. The SERDES control signals are present in variations targeting devices with GX transceivers. For Stratix

II GX and Arria GX devices, the reconfiguration signals—reconfig_clk, reconfig_togxb, and

reconfig_fromgxb—are included only when the Enable transceiver dynamic reconfiguration option is

turned on. The reconfiguration signals—

gxb_cal_blk_clk

,

pcs_pwrdwn_out

,

gxb_pwrdn_in

,

reconfig_clk

, and

reconfig_busy

—are not present in variations targeting Stratix V devices with GX

transceivers.

Altera Corporation

Interface Signals

7-25

10/100/1000 Multiport Ethernet MAC with 1000BASE-X/SGMII PCS and Embedded PMA

UG-01008

2014.06.30