Altera Triple Speed Ethernet MegaCore Function User Manual

Page 88

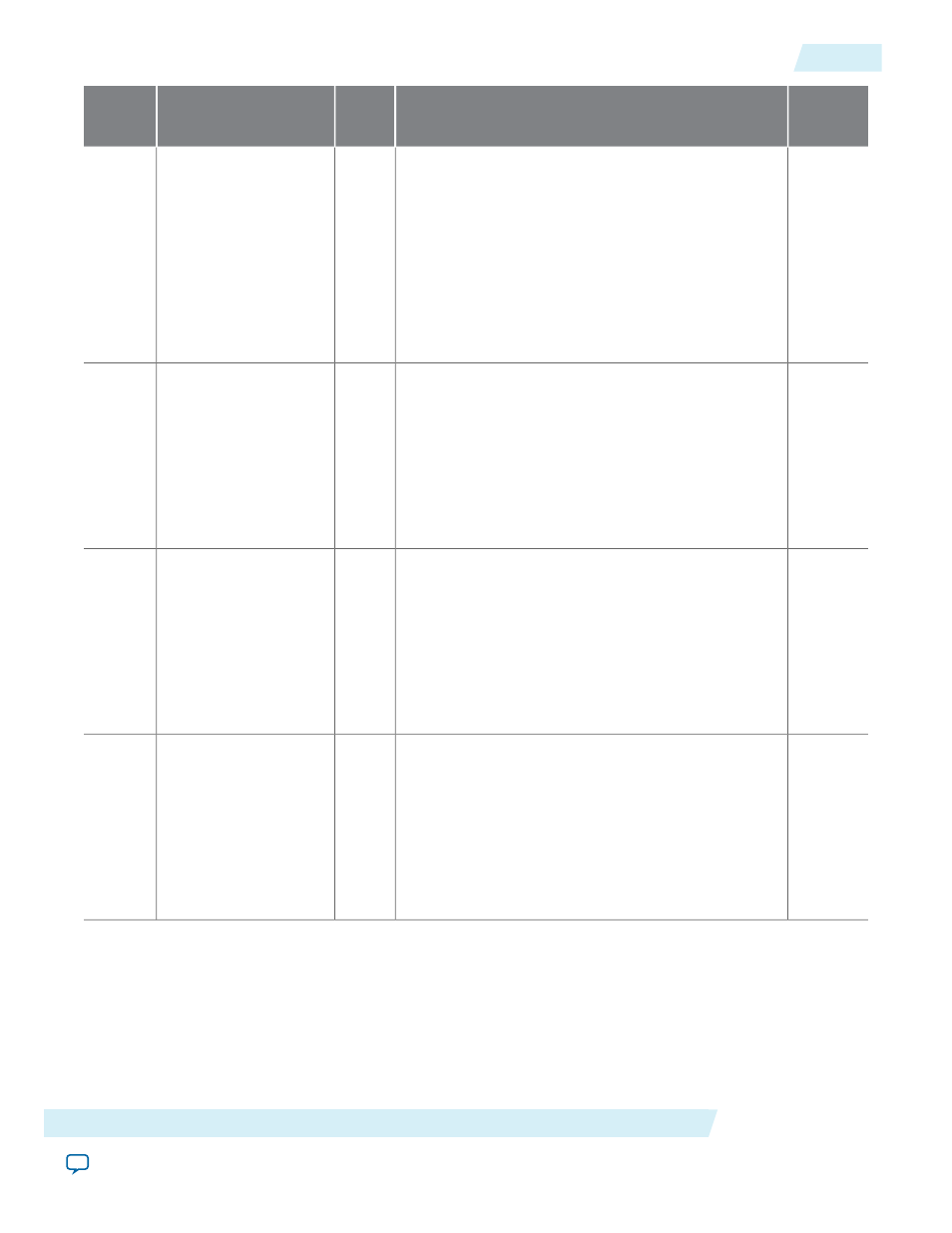

HW Reset

Description

R/W

Name

Dword

Offset

0

Variable-length section-full threshold of the transmit

FIFO buffer. Use the depth of your FIFO buffer to

determine this threshold.

For cut-through mode, this threshold is typically set to

16. Set this threshold to a value above the

tx_almost_

empty

threshold.

For store-and-forward mode, set this threshold to 0.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value of 16.

RW/

RO

tx_section_full

0x0A

0

Variable-length almost-empty threshold of the receive

FIFO buffer. Use the depth of your FIFO buffer to

determine this threshold.

Due to internal pipeline latency, you must set this

threshold to a value greater than 3. This threshold is

typically set to 8.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value of 8.

RW/

RO

rx_almost_empty

0x0B

0

Variable-length almost-full threshold of the receive FIFO

buffer. Use the depth of your FIFO buffer to determine

this threshold.

Due to internal pipeline latency, you must set this

threshold to a value greater than 3. This threshold is

typically set to 8.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value of 8.

RW/

RO

rx_almost_full

0x0C

0

Variable-length almost-empty threshold of the transmit

FIFO buffer. Use the depth of your FIFO buffer to

determine this threshold.

Due to internal pipeline latency, you must set this

threshold to a value greater than 3. This threshold is

typically set to 8.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value of 8.

RW/

RO

tx_almost_empty

0x0D

Altera Corporation

Configuration Register Space

6-5

Base Configuration Registers (Dword Offset 0x00 – 0x17)

UG-01008

2014.06.30