Mac architecture, Mac architecture -2 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 38

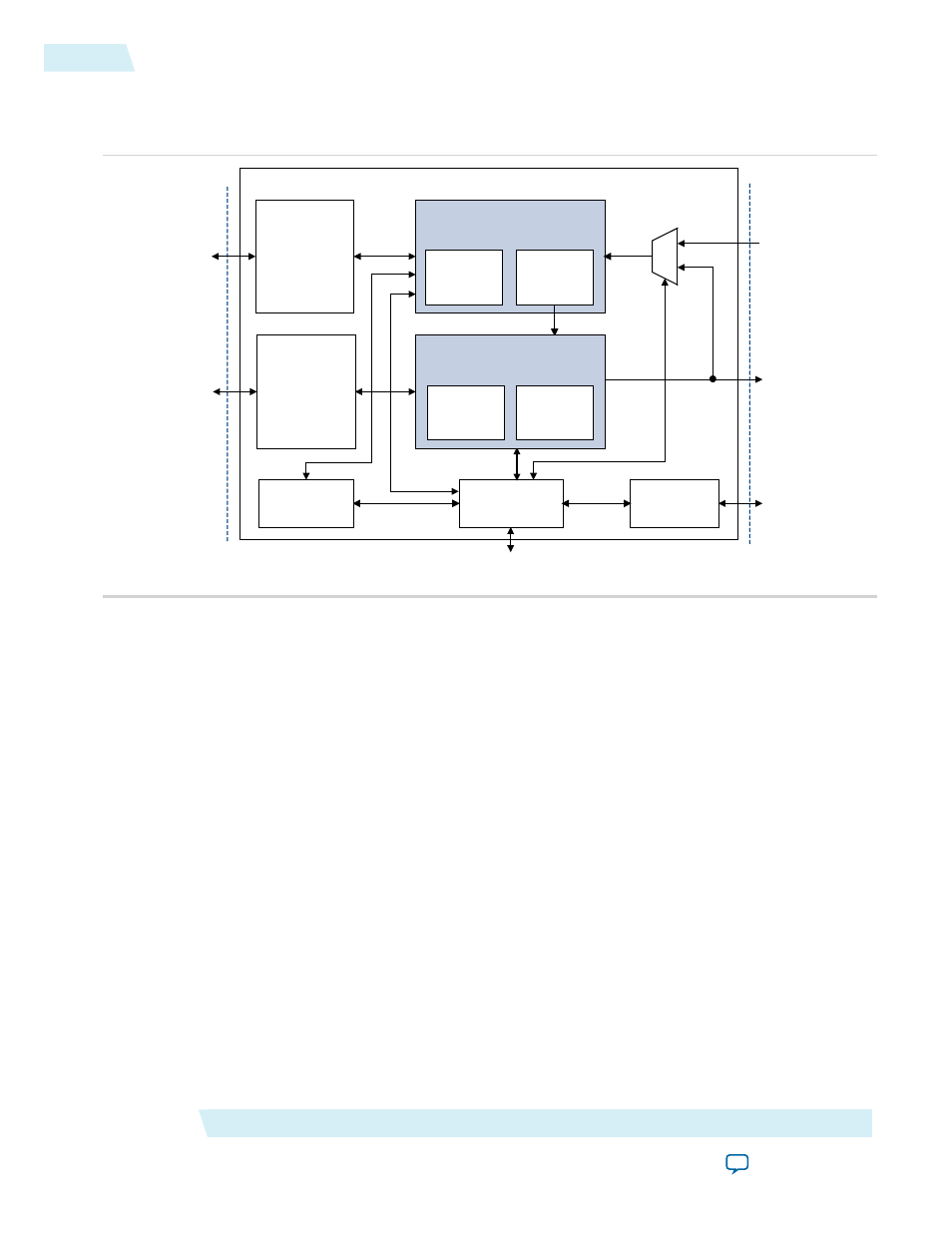

MAC Architecture

Figure 4-1: 10/100/1000 Ethernet MAC With Internal FIFO Buffers

Receive

FIFO Buffer

Transmit

FIFO Buffer

Configuration and

Statistics

MDIO Master

CRC Check

Pause

Frame

Termination

MII/GMII /RGMII

Receive

Local

Loopback

Receiver Control

MII/GMII /RGMII

Transmit

PHY

Management

Interface

Control Interface

(Avalon -MM)

Magic Packet

Detection

Ethernet Side

System Side

CRC

Generation

Pause

Frame

Generation

Transmitter Control

MAC Transmit

Interface

(Avalon-ST)

MAC Receive

Interface

(Avalon-ST)

10/100/1000 Ethernet MAC with Internal FIFO Buffers

The FIFO buffers, which you can configure to 8- or 32-bits wide, store the transmit and receive data. The

buffer width determines the data width on the Avalon-ST receive and transmit interfaces. You can configure

the FIFO buffers to operate in cut-through or store-and-forward mode using the

rx_section_full

and

tx_section_full

registers.

Functional Description

Altera Corporation

UG-01008

MAC Architecture

4-2

2014.06.30