Frame writing, Ip payload alignment, Mac transmit and receive latencies – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 47: Mac transmit and receive latencies -11

• Stacked VLAN tagged frames—the payload length is between 38 (0x26) and 1536 (0x0600), excluding

1536.

If the frame or payload length is not valid, the MAC function asserts one of the following signals to indicate

length error:

•

rx_err[1]

in MACs with internal FIFO buffers.

•

data_rx_error[0]

in MACs without internal FIFO buffers.

Frame Writing

The MegaCore function removes the preamble and SFD fields from the frame. The CRC field and padding

bytes may be removed depending on the configuration.

For MAC variations with internal FIFO buffers, the MAC function writes the frame to the internal receive

FIFO buffers.For MAC variations without internal FIFO buffers, it forwards the frame to the Avalon-ST

receive interface.

MAC variations without internal FIFO buffers do not support backpressure on the Avalon-ST receive

interface. In this variation, if the receiving component is not ready to receive data from the MAC function,

the frame gets truncated with error and subsequent frames are also dropped with error.

IP Payload Alignment

The network stack makes frequent use of the IP addresses stored in Ethernet frames. When you turn on the

Align packet headers to 32-bit boundaries option, the MAC function aligns the IP payload on a 32-bit

boundary by adding two bytes to the beginning of Ethernet frames. The padding of Ethernet frames are

determined by the registers

tx_cmd_stat

and

rx_cmd_stat

on transmit and receive, respectively.

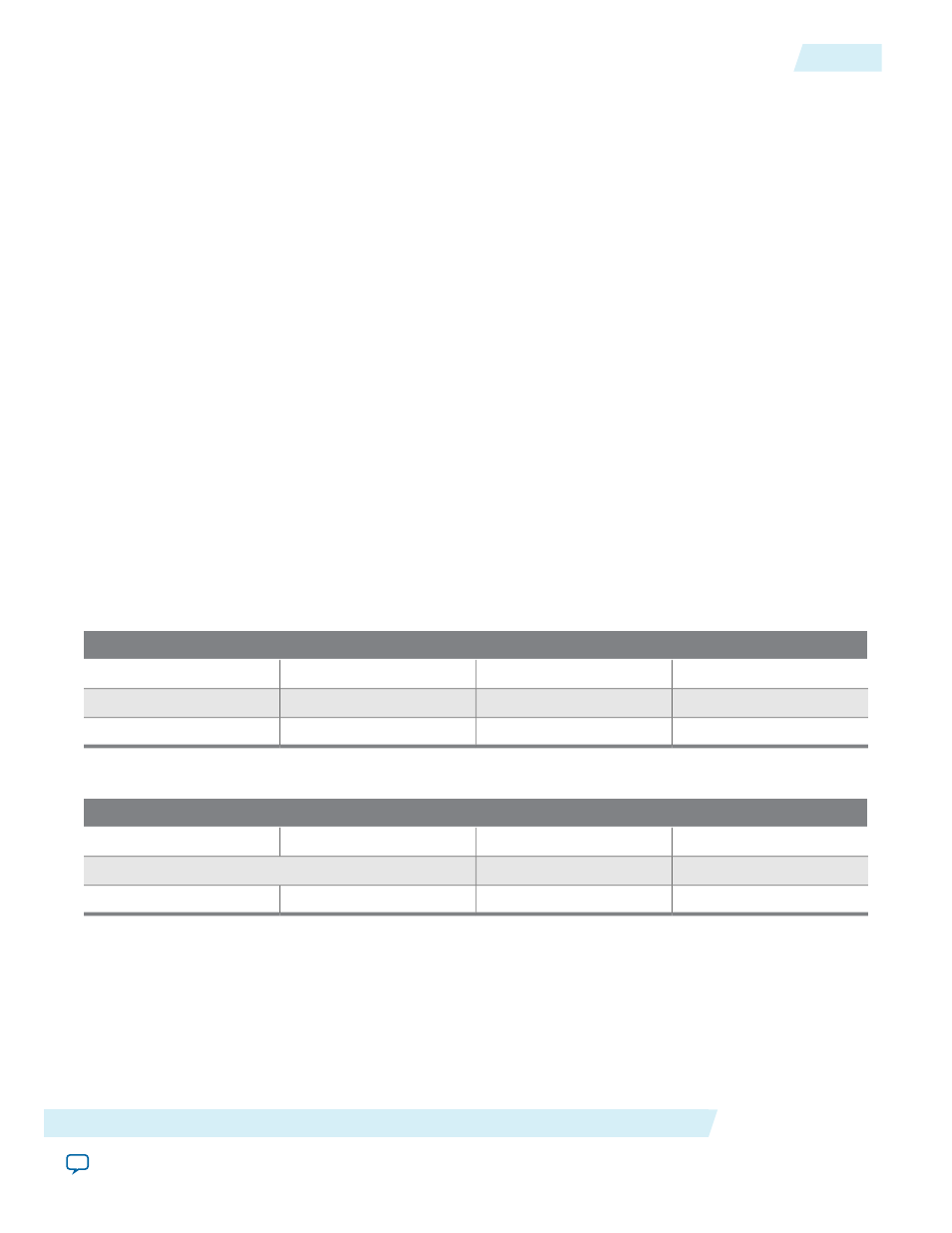

Table 4-3: 32-Bit Interface Data Structure — Non-IP Aligned Ethernet Frame

Bits

7...0

15...8

23...16

31...24

Byte 3

Byte 2

Byte 1

Byte 0

Byte 7

Byte 6

Byte 5

Byte 4

Table 4-4: 32-Bit Interface Data Structure — IP Aligned Ethernet Frame

Bits

7...0

15...8

23...16

31...24

Byte 1

Byte 0

padded with zeros

Byte 5

Byte 4

Byte 3

Byte 2

MAC Transmit and Receive Latencies

Altera uses the following definitions for the transmit and receive latencies:

• Transmit latency is the number of clock cycles the MAC function takes to transmit the first bit on the

network-side interface (MII/GMII/RGMII) after the bit was first available on the Avalon-ST interface.

• Receive latency is the number of clock cycles the MAC function takes to present the first bit on the Avalon-

ST interface after the bit was received on the network-side interface (MII/GMII/RGMII).

Altera Corporation

Functional Description

4-11

Frame Writing

UG-01008

2014.06.30