Altera Triple Speed Ethernet MegaCore Function User Manual

Page 91

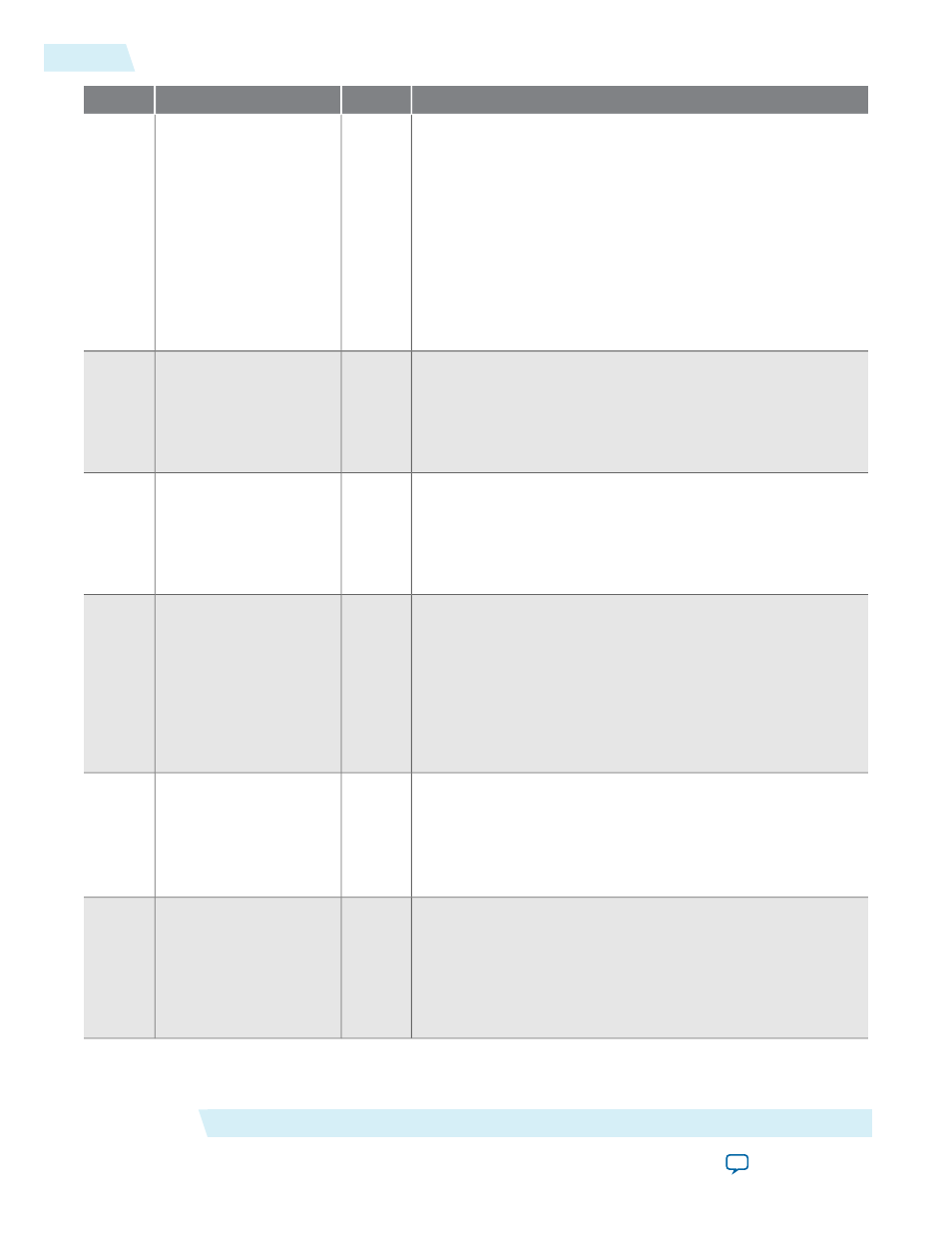

Description

R/W

Name

Bit(s)

CRC forwarding on receive.

• Set this bit to 1 to forward the CRC field to the user

application.

• Set this bit to 0 to remove the CRC field from receive frames

before the MAC function forwards the frame to the user

application.

• The MAC function ignores this bit when it receives a padded

frame and the

PAD_EN

bit is 1. In this case, the MAC

function checks the CRC field and removes the checksum

and padding from the frame before forwarding the frame

to the user application.

RW

CRC_FWD

6

Pause frame forwarding on receive.

• Set this bit to 1 to forward receive pause frames to the user

application.

• Set this bit to 0 to terminate and discard receive pause

frames.

RW

PAUSE_FWD

7

Pause frame processing on receive.

• Set this bit to 1 to ignore receive pause frames.

• Set this bit to 0 to process receive pause frames. The MAC

function suspends transmission for an amount of time

specified by the pause quanta.

RW

PAUSE_IGNORE

8

MAC address on transmit.

• Set this bit to 1 to overwrite the source MAC address in

transmit frames received from the user application with the

MAC primary or supplementary address configured in the

registers. The

TX_ADDR_SEL

bit determines the address

selection.

• Set this bit to 0 to retain the source MAC address in transmit

frames received from the user application.

RW

TX_ADDR_INS

9

Half-duplex enable.

• Set this bit to 1 to enable half-duplex.

• Set this bit to 0 to enable full-duplex.

• The MAC function ignores this bit if you set the

ETH_SPEED

bit to 1.

RW

HD_ENA

10

Excessive collision condition.

• The MAC function sets this bit to 1 when it discards a frame

after detecting a collision on 16 consecutive frame retrans-

missions.

• The MAC function clears this bit following a hardware or

software reset. See the

SW_RESET

bit description.

RO

EXCESS_COL

11

Configuration Register Space

Altera Corporation

UG-01008

Command_Config Register (Dword Offset 0x02)

6-8

2014.06.30