Figure 7-24: type 2 egress correction field update – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 161

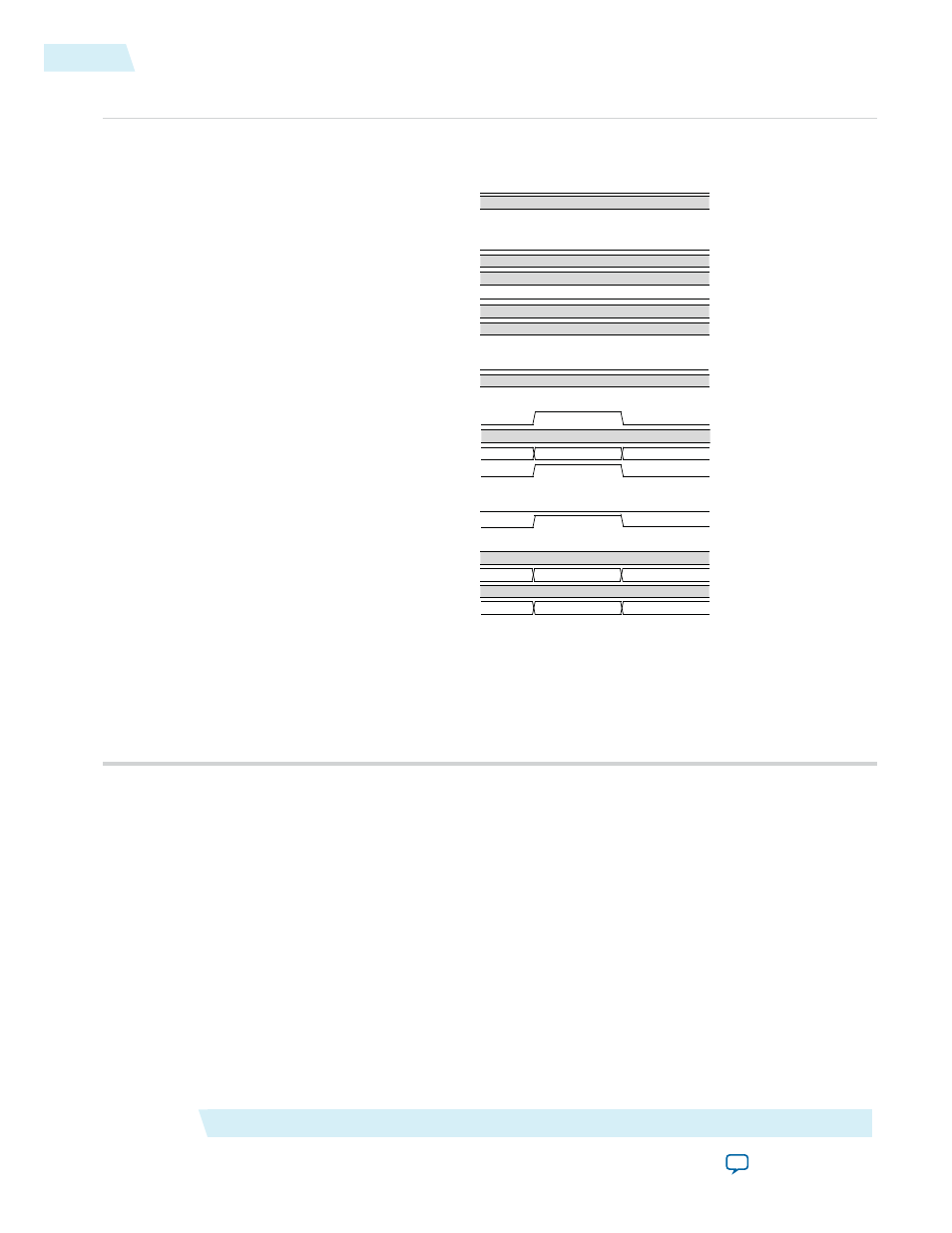

Figure 7-24: Type 2 Egress Correction Field Update

Type 2 Egress Correction Field Update, 64b, IPV6

2-step Timestamp Request,Input

tx_egress_timestamp_request_valid

tx_egress_timestamp_request_data[N:0]

2-step Timestamp Return,Output

tx_egress_timestamp_96b_valid

tx_egress_timestamp_96b_fingerprint[N:0]

tx_egress_timestamp_96b_data[95:0]

tx_egress_timestamp_64b_valid

tx_egress_timestamp_64b_fingerprint[N:0]

tx_egress_timestamp_64b_data[63:0]

1-step Timestamp Insert,Input

tx_etstamp_ins_ctrl_timestamp_insert

tx_etstamp_ins_ctrl_timestamp_format

1-step Residence Time Update,Input

tx_etstamp_ins_ctrl_residence_time_update

tx_etstamp_ins_ctrl_ingress_timestamp_96b[95:0]

tx_etstamp_ins_ctrl_ingress_timestamp_64b[63:0]

tx_etstamp_ins_ctrl_residence_time_calc_format

1-step IPv4 and IPv6 Checksum,Input

tx_etstamp_ins_ctrl_checksum_zero

tx_etstamp_ins_ctrl_checksum_correct

1-step Location Offset,Input

tx_etstamp_ins_ctrl_offset_timestamp[15:0]

Offset 1

tx_etstamp_ins_ctrl_offset_correction_field[15:0]

Offset 2

tx_etstamp_ins_ctrl_offset_checksum_field[15:0]

tx_etstamp_ins_ctrl_offset_checksum_correction[15:0]

64’b0

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

shows the TX timestamp signals for the IEEE 1588v2 feature in a two step operation.

When the

tx_egress_timestamp_request_valid

signal is driven high with a unique fingerprint, the MAC

returns an egress timestamp associated with that unique fingerprint. The signals related to the 1-step operation

can be driven low or ignored. There is no modification to the packet content.

Interface Signals

Altera Corporation

UG-01008

IEEE 1588v2 Timestamp

7-46

2014.06.30