Altera Triple Speed Ethernet MegaCore Function User Manual

Page 114

PCS Control Register = 0x9140

Wait PCS Control Register RESET bit is clear

3. MAC Configuration Register Initialization

Refer to step 2 in

Triple-Speed Ethernet System with MII/GMII or RGMII

on page 6-28.

If 1000BASE-X/SGMII PCS is initialized, set the

ETH_SPEED

(bit 3) and

ENA_10

(bit 25) in

command_config

register to 0. If half duplex is reported in the PHY/PCS status register, set the

HD_ENA

(bit 10) to 1 in

command_config

register.

Note:

Triple-Speed Ethernet System with 1000BASE-X Interface

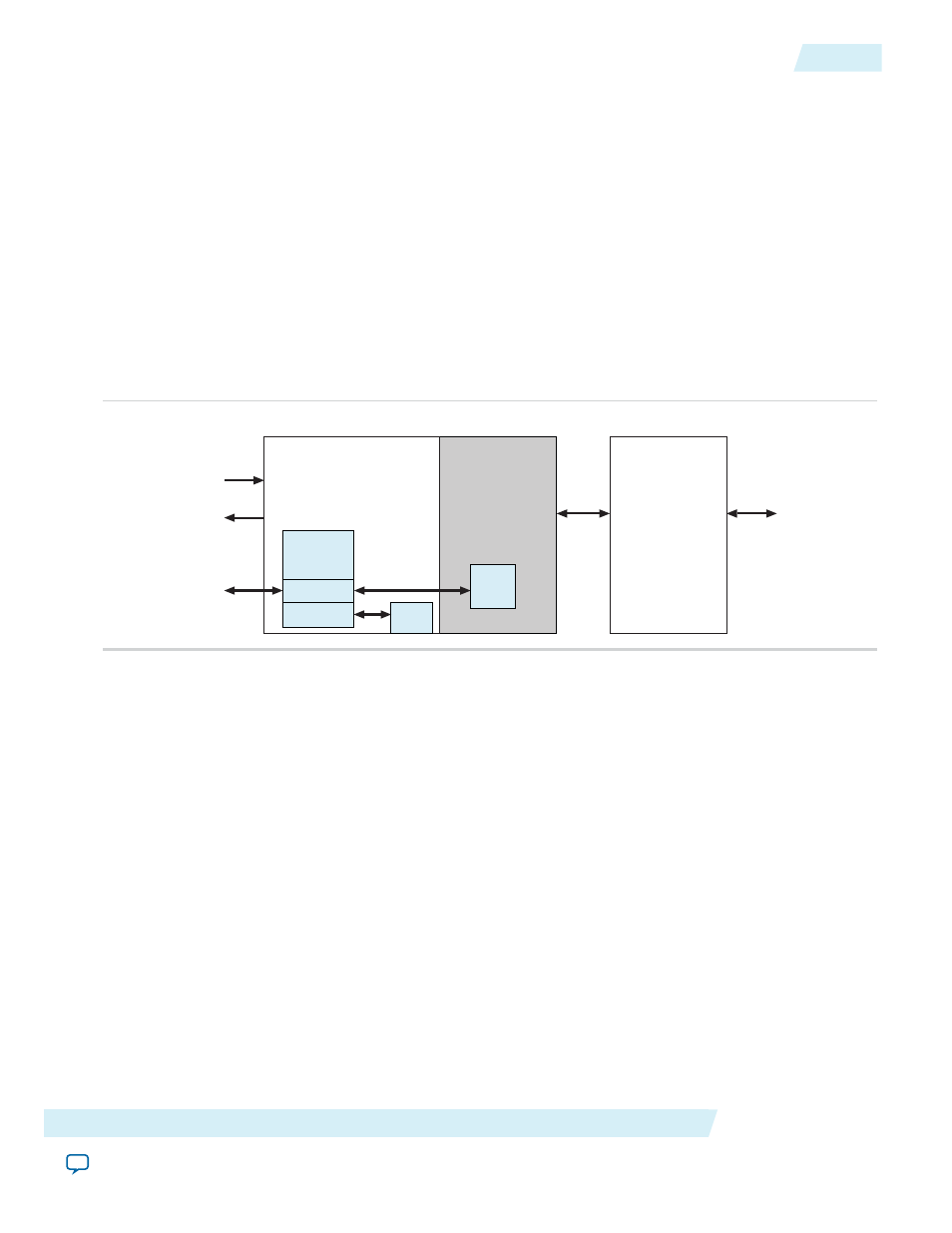

Figure 6-4: Triple-Speed Ethernet System with 1000BASE-X Interface with Register Initialization

Recommendation

10/100/1000 Mbps MAC

1000BASE-X

Optical

Tranceiver (SFP)

MAC

Register

Space

MDIO Space 0

MDIO Space 1

MDIO

Host

Avalon ST TX

Avalon ST RX

Avalon MM

Fiber

Interface

1000BASE-X Interface (1.25 Gbps)

1000BASE-X/

SGMII PCS

PCS

Register

Space

Use the following recommended initialization sequences for the example in

Figure 6–5

.

1. External PHY Initialization using MDIO

Refer to step 1 in

Triple-Speed Ethernet System with MII/GMII or RGMII

on page 6-28.

2. PCS Configuration Register Initialization

a. Set Auto Negotiation Link Timer

//Set Link timer to 10ms for 1000BASE-X

link_timer (address offset 0x12) = 0x12D0

link_timer (address offset 0x13) = 0x13

b. Configure SGMII

//1000BASE-X/SGMII PCS is default in 1000BASE-X Mode

//SGMII_ENA = 0, USE_SGMII_AN = 0

if_mode = 0x0000

c. Enable Auto Negotiation

//Enable Auto Negotiation

Altera Corporation

Configuration Register Space

6-31

Triple-Speed Ethernet System with 1000BASE-X Interface

UG-01008

2014.06.30