Register initialization, Register initialization -27 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 110

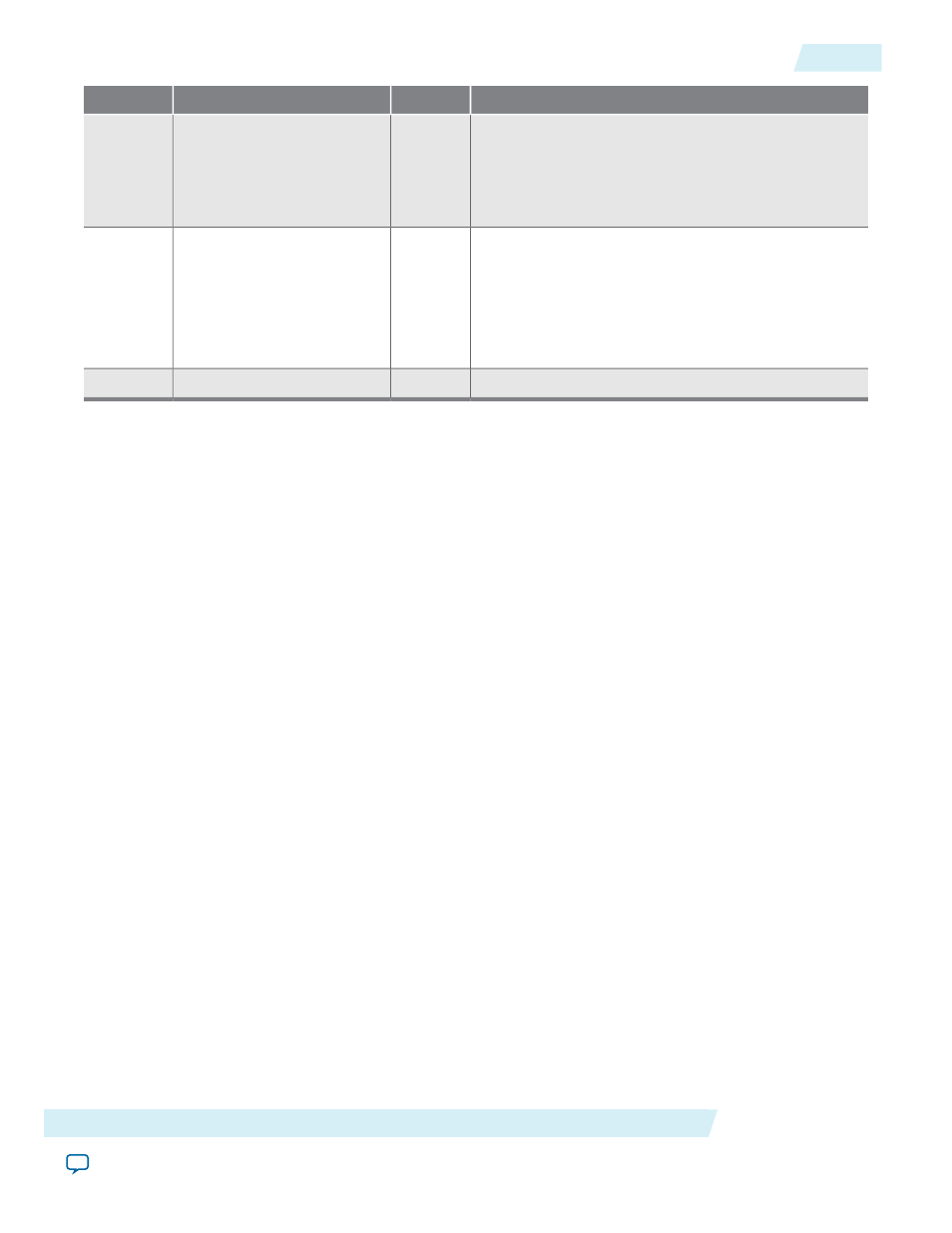

Description

R/W

Name

Bit(s)

SGMII half-duplex mode. Setting this bit to 1 enables

half duplex for 10/100 Mbps speed. This bit is ignored

when

SGMII_ENA

is 0 or

USE_SGMII_AN

is 1. These bits

are only valid if you only enable the SGMII mode and

not the auto-negotiation mode.

RW

SGMII_DUPLEX

4

SGMII auto-negotiation mode:

• 1: enable SGMII PHY mode

• 0: enable SGMII MAC mode

This bit resets to 0, which defaults to SGMII MAC

mode.

RW

SGMII_AN_MODE

5

—

—

Reserved

15:6

Register Initialization

The Triple-Speed Ethernet MegaCore function supports various types of interface commonly used by the

following Ethernet solutions:

• MII/GMII

• RGMII

• 10-bit Interface

• SGMII

• 1000BASE-X

• Management Data Input/Output (MDIO) for external PHY register configuration

When using the Triple-Speed Ethernet MegaCore function with an external interface, you must understand

the requirements and initialize the registers.

Register initialization mainly performed in the following configurations:

• External PHY Initialization using MDIO (Optional)

• PCS Configuration Register Initialization

• MAC Configuration Register Initialization

This section discusses the register initialization for the following examples of the Ethernet system using

different MAC interfaces with recommended initialization sequences:

•

Triple-Speed Ethernet System with MII/GMII or RGMII

on page 6-28

•

Triple-Speed Ethernet System with SGMII

on page 6-30

•

Triple-Speed Ethernet System with 1000BASE-X Interface

on page 6-31

Altera Corporation

Configuration Register Space

6-27

Register Initialization

UG-01008

2014.06.30