Altera Triple Speed Ethernet MegaCore Function User Manual

Page 167

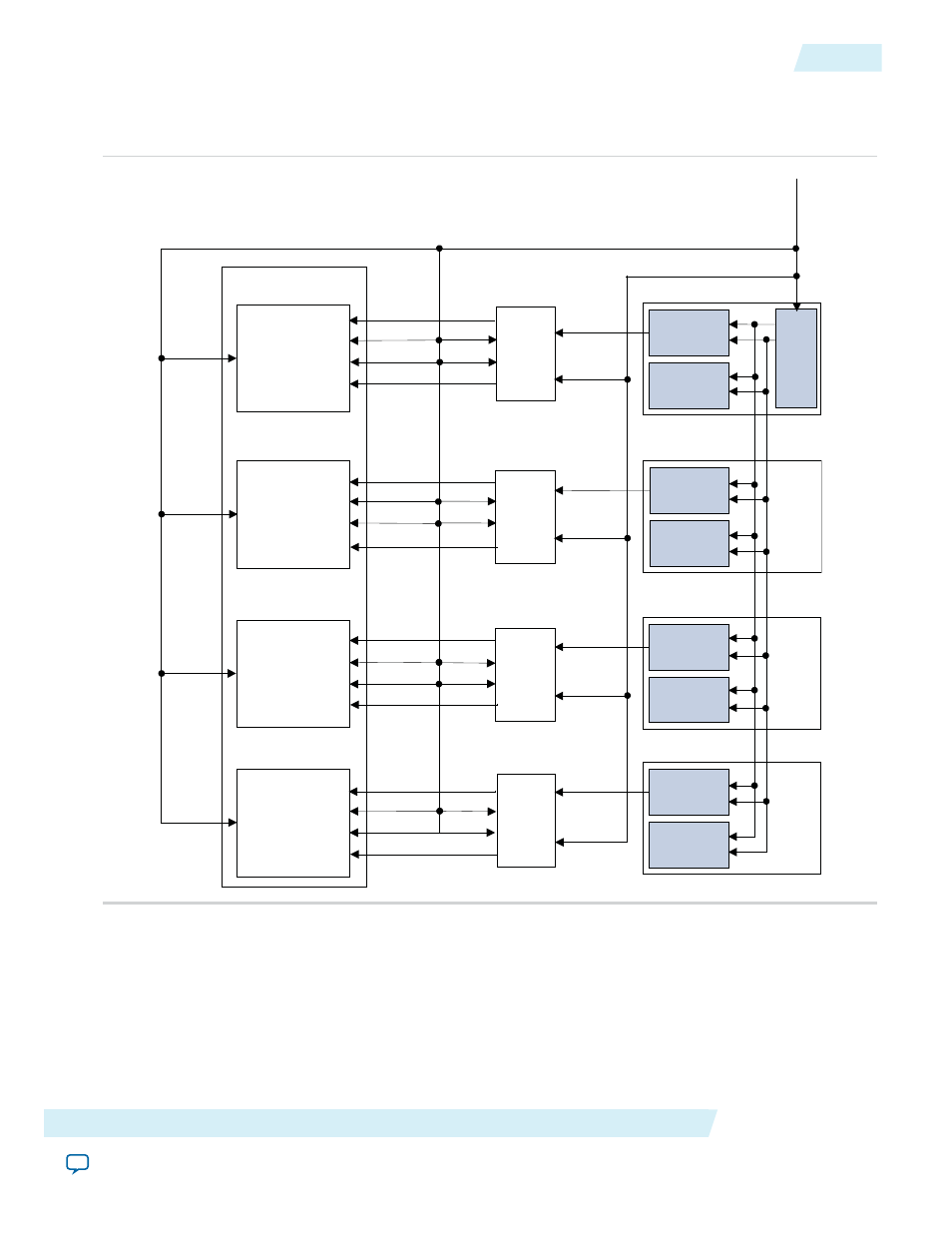

Figure 8-3: Clock Distribution in MAC and SGMII PCS with LVDS Configuration—Optimal Case

Figure shows the optimal clock distribution scheme you can achieve in configurations that contain the MAC,

SGMII PCS and LVDS Soft-CDR I/O.

tbi _tx _clk

tbi _ rx _ clk 1

tbi _ rx _ clk 2

tbi _ rx _clk 3

tbi _ rx _clk 4

clk 1

clk 2

clk 3

clk 4

PCS 1

rx _clk 1

tx _ clk 1

PCS 2

rx _clk 2

tx _ clk 2

PCS 3

rx _clk 3

tx _ clk 3

PCS 4

rx _clk 4

tx _ clk 4

4 -port

MAC

Port 1

ref _ clk

ALTLVDS _ RX _

COMPONENT

ALTLVDS _TX _

COMPONENT

PLL

ALTLVDS _ RX _

COMPONENT

ALTLVDS _TX _

COMPONENT

ALTLVDS _ RX _

COMPONENT

ALTLVDS _TX _

COMPONENT

ALTLVDS _ RX _

COMPONENT

ALTLVDS _TX _

COMPONENT

pll

pll ~ clk 1

rx _ clk 1

tx _ clk 1

rx _ clk 2

tx _ clk 2

rx _ clk 3

tx _ clk 3

rx _ clk 4

tx _ clk 4

Port 2

Port 3

Port 4

tx _ clk _ en 1

rx _clk _ en 1

tx _ clk _en 2

rx _clk _en 2

tx _ clk _en 3

rx _clk _en 3

tx _ clk _en 4

rx _clk _en 4

Altera Corporation

Design Considerations

8-5

MAC and PCS With LVDS Soft-CDR I/O

UG-01008

2014.06.30