Sharing plls in devices with lvds soft-cdr i/o, Sharing plls in devices with gige phy, Tx_p – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 168: Rx_p, Ref_clk, Sharing plls in devices with lvds soft-cdr i/o 8-6

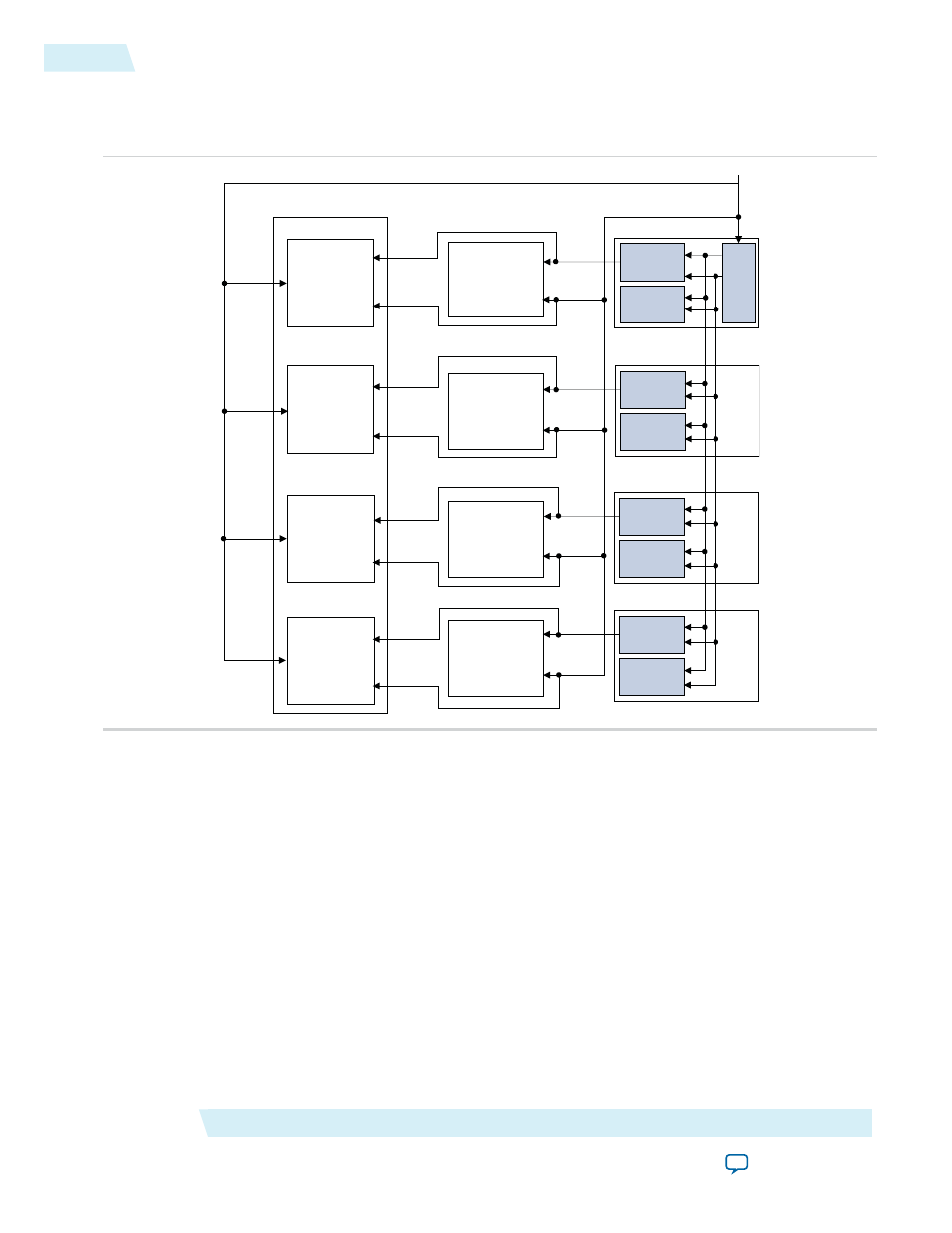

Figure 8-4: Clock Distribution in MAC and 1000BASE-X PCS with LVDS Configuration—Optimal Case

Figure shows the optimal clock distribution scheme you can achieve in configurations that contain the MAC,

1000BASE-X PCS, and LVDS Soft-CDR I/O.

Port 1

4 -port MAC

tbi _tx _ clk

tbi _rx _ clk 1

tbi _rx _ clk 2

tbi _rx _clk 3

tbi _rx _clk 4

rx _clk 1

tx _ clk 1

rx _ clk 2

tx _ clk 2

rx _ clk 3

tx _ clk 3

Port 4

Port 3

rx _ clk 4

tx _ clk 4

clk 1

clk 2

clk 3

clk 4

PCS 1

PCS 2

PCS 3

PCS 4

ref _ clk

ALTLVDS _ RX _

COMPONENT

ALTLVDS _ TX _

COMPONENT

PLL

ALTLVDS _ RX _

COMPONENT

ALTLVDS _ TX _

COMPONENT

ALTLVDS _ RX _

COMPONENT

ALTLVDS _ TX _

COMPONENT

ALTLVDS _ RX _

COMPONENT

ALTLVDS _ TX _

COMPONENT

pll

pll ~clk 1

Port 2

Sharing PLLs in Devices with LVDS Soft-CDR I/O

For designs that contain multiple instances of MAC and PCS with PMA or PCS with PMA variation targeting

devices with LVDS soft-CDR I/O, you can optimize resource utilization by sharing the PLLs.

The Quartus II software merges the PLLs for these instances if you implement the following items in your

design:

• Connect the reference clock of each instance to the same source.

• Place the LVDS I/O pins on the same side of the FPGA.

Sharing PLLs in Devices with GIGE PHY

For Cyclone V designs that contain multiple instances of MAC and PCS with PMA or PCS with PMA

variation targeting devices with GIGE PHY, you can share the PLLs by placing the associated signals (

tx_p

,

rx_p

, and

ref_clk

) to the same I/O block of transceiver bank through pin assignment. Additionally, the

Design Considerations

Altera Corporation

UG-01008

Sharing PLLs in Devices with LVDS Soft-CDR I/O

8-6

2014.06.30