Release information, Release information -11 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 18

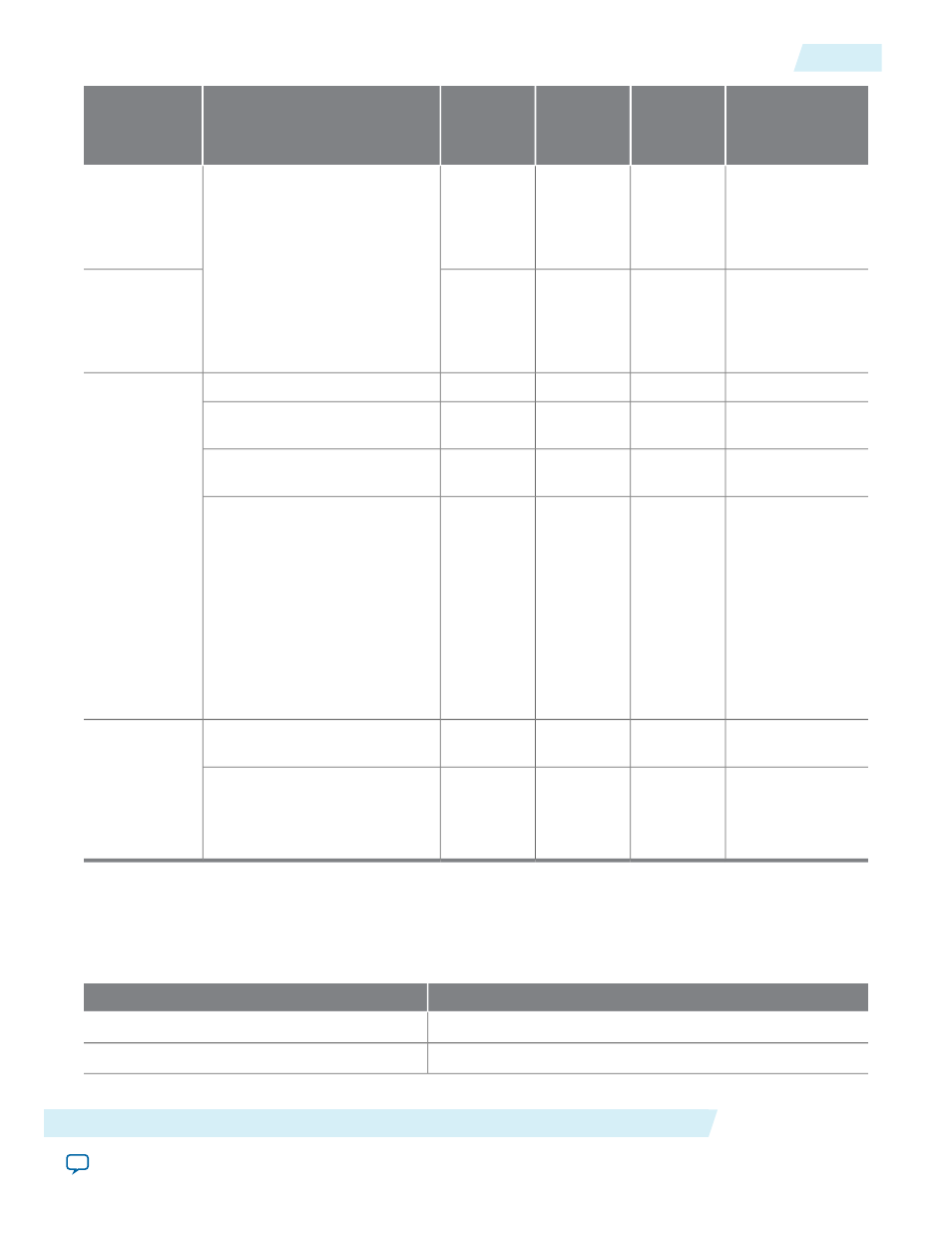

Memory

(M20K Blocks/ MLAB

Bits)

Logic

Registers

Combina-

tional ALUTs

FIFO Buffer

Size (Bits)

Settings

MegaCore

Function

60/24576

48365

35303

—

MII/GMII All MAC options

enabled

12-port 10/

100/1000-

Mbps

Ethernet

MAC

120/49152

96092

70079

—

24-port 10/

100/1000-

Mbps

Ethernet

MAC

0/0

786

614

—

1000BASE-X

1000BASE-

X/SGMII

PCS

0/480

1160

839

—

1000BASE-X SGMII bridge

enabled

0/480

1250

857

—

1000BASE-X SGMII bridge

enabled PMA block (LVDS_IO)

5/2208

1991

2203

—

1000BASE-X SGMII bridge

enabled PMA block (GXB)

(reconfig controller has been

compiled together with

1000BASE-X SGMII bridge

enabled PMA block (GXB))

Combinational ALUTs =1441,

Logic Registers = 903 and

Memory(M20K Block/MLAB

Bits) = 4/~2048

16/1248

6132

4306

2048×32

All MAC options enabled SGMII

bridge enabled

10/100/

1000-Mbps

Ethernet

MAC and

1000BASE-

X/SGMII

PCS

4/1536

5318

5062

0

Default MAC option SGMII

bridge enabled IEEE 1588v2

feature enabled

Release Information

Table 1-6: Triple-Speed Ethernet MegaCore Function Release Information

Description

Item

14.0

Version

June 2014

Release Date

Altera Corporation

About This MegaCore Function

1-11

Release Information

UG-01008

2014.06.30