Base configuration registers (dword offset 0x00, 0x17) – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 86

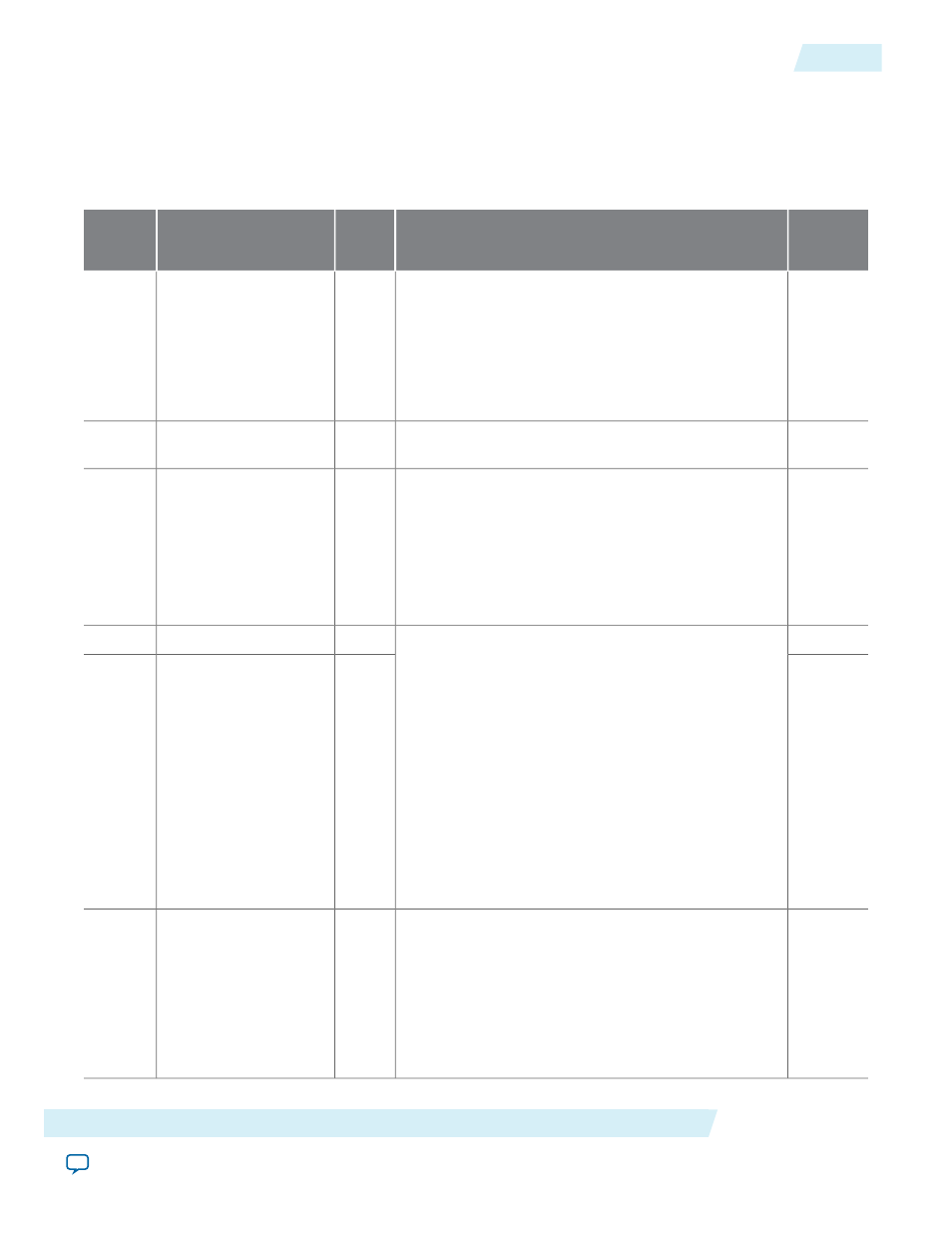

Base Configuration Registers (Dword Offset 0x00 – 0x17)

lists the base registers you can use to configure the MAC function. A software reset does not reset

these registers except the first two bits (

TX_ENA

and

RX_ENA

= 0) in the

command_config

register.

Table 6-2: Base Configuration Register Map

HW Reset

Description

R/W

Name

Dword

Offset

<IP

version

number>

• Bits[15:0]—Set to the current version of the MegaCore

function.

• Bits[31:16]—Customer specific revision, specified by

the

CUST_VERSION

parameter defined in the top-level

file generated for the instance of the MegaCore

function. These bits are set to 0 during the configura-

tion of the MegaCore function.

RO

rev

0x00

0

Scratch register. Provides a memory location for you to

test the device memory operation.

RW

scratch

0x01

0

MAC configuration register. Use this register to control

and configure the MAC function. The MAC function

starts operation as soon as the transmit and receive enable

bits in this register are turned on. Altera, therefore,

recommends that you configure this register last.

See

Command_Config Register (Dword Offset 0x02)

on page 6-7 for the bit description.

RW

command_config

0x02

0

6-byte MAC primary address. The first four most

significant bytes of the MAC address occupy

mac_0

in

reverse order. The last two bytes of the MAC address

occupy the two least significant bytes of

mac_1

in reverse

order.

For example, if the MAC address is 00-1C-23-17-4A-CB,

the following assignments are made:

mac_0

= 0x17231c00

mac_1

= 0x0000CB4a

Ensure that you configure these registers with a valid

MAC address if you disable the promiscuous mode

(

PROMIS_EN

bit in

command_config

= 0).

RW

mac_0

0x03

0

RW

mac_1

0x04

1518

• Bits[15:0]—16-bit maximum frame length in bytes.

The MegaCore function checks the length of receive

frames against this value. Typical value is 1518.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the maximum frame length is fixed

to 1518.

• Bits[31:16]—unused.

RW/

RO

frm_length

0x05

Altera Corporation

Configuration Register Space

6-3

Base Configuration Registers (Dword Offset 0x00 – 0x17)

UG-01008

2014.06.30