Mac transmit interface signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 121

Description

Bit

Indicates broadcast frames. Asserted with

ff_rx_sop

and remains asserted until the end of

the frame.

2

Indicates multicast frames. Asserted with

ff_rx_sop

and remains asserted until the end of

the frame.

1

Indicates unicast frames. Asserted with

ff_rx_sop

and remains asserted until the end of

the frame.

0

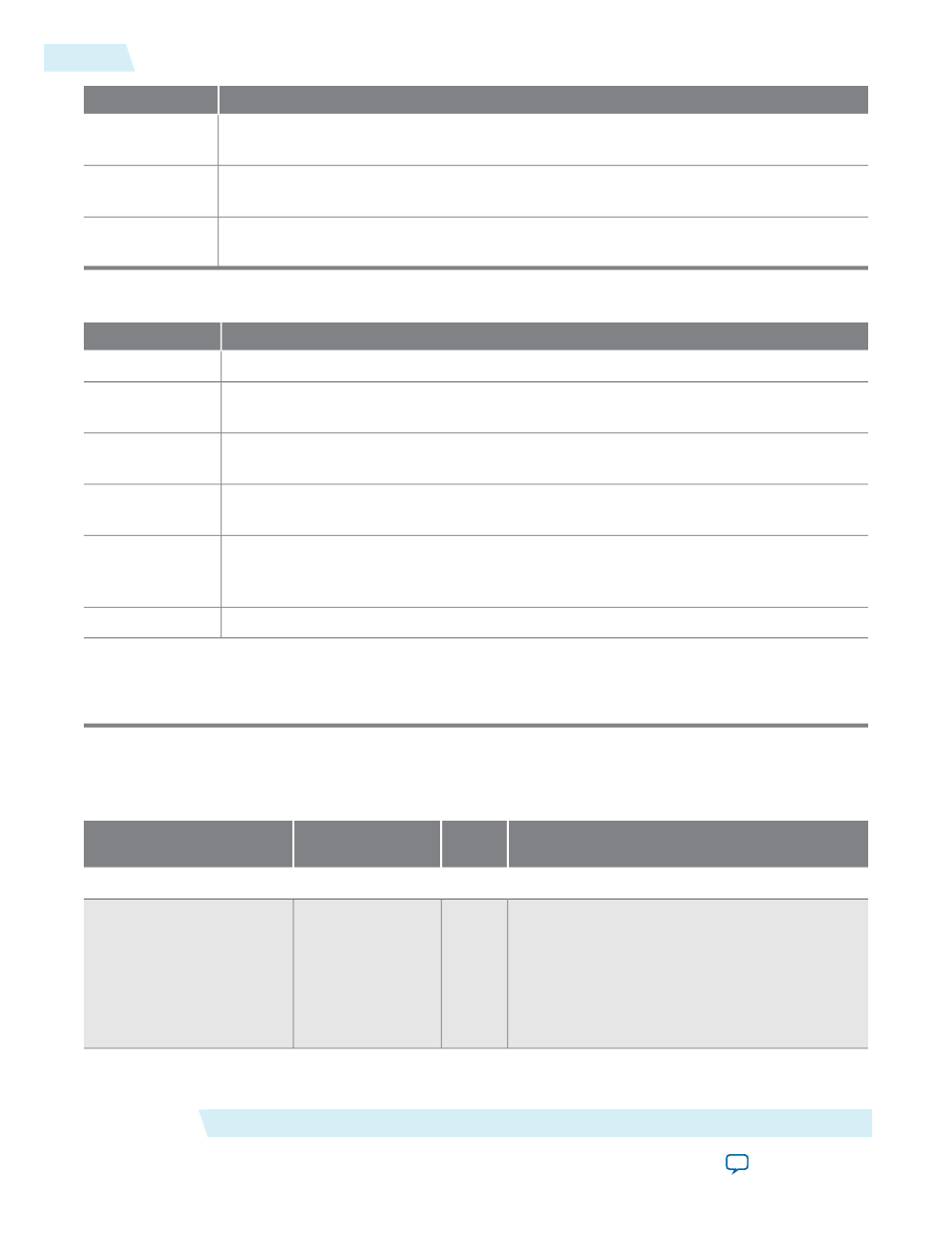

Table 7-7: rx_err Bit Description

Description

Bit

Collision error. Asserted when the frame was received with a collision.

5

Corrupted receive frame caused by PHY or PCS error. Asserted when the error is detected

on the MII/GMII/RGMII.

4

Truncated receive frame. Asserted when the receive frame is truncated due to an overflow

in the receive FIFO buffer.

3

CRC error. Asserted when the frame is received with a CRC-32 error. This error bit applies

only to frames with a valid length. Refer to

on page 4-10.

2

Invalid length error. Asserted when the receive frame has an invalid length as defined by

the IEEE Standard 802.3. For more information on the frame length, refer to

on page 4-10 .

1

Receive frame error. Indicates that an error has occurred. It is the logical OR of

rx_err

[5:1].

0

Note to

:

1. Bits 1 and 2 are not mutually exclusive. Ignore CRC error

rx_err[2]

signal if it is asserted at the same

time as the invalid length error

rx_err[1]

signal.

MAC Transmit Interface Signals

Table 7-8: MAC Transmit Interface Signals

Description

I/O

Avalon-ST Signal

Type

Name

Avalon-ST Signals

Transmit clock. All transmit signals are

synchronized on the rising edge of this clock.

Set this clock to the required frequency to get the

desired bandwidth on the Avalon-ST transmit

interface. This clock can be completely indepen-

dent from

tx_clk

.

I

clk

ff_tx_clk

Interface Signals

Altera Corporation

UG-01008

MAC Transmit Interface Signals

7-6

2014.06.30